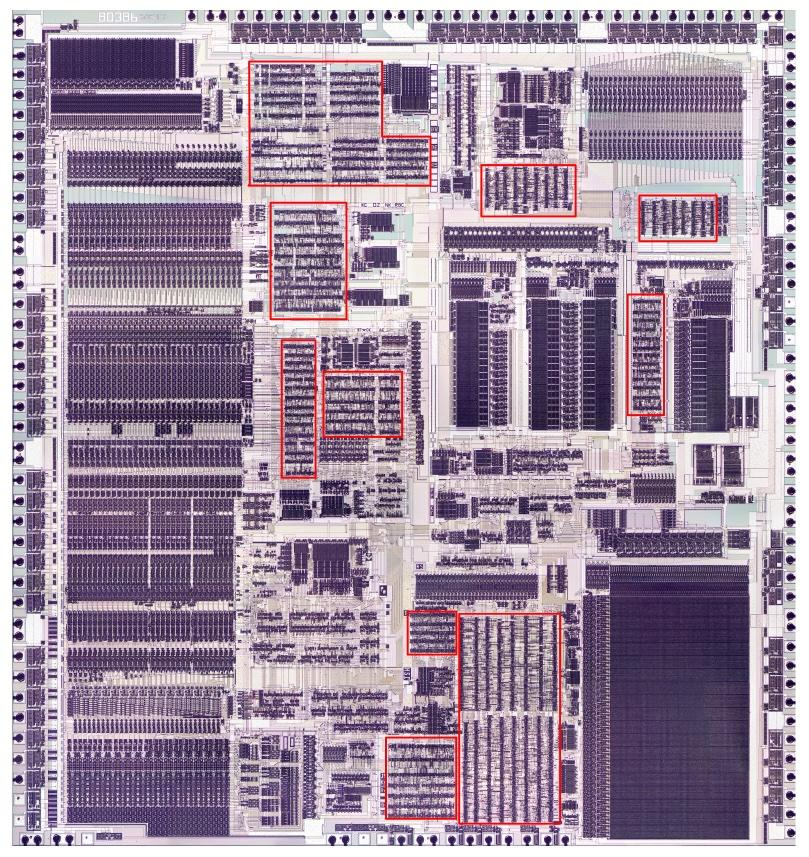

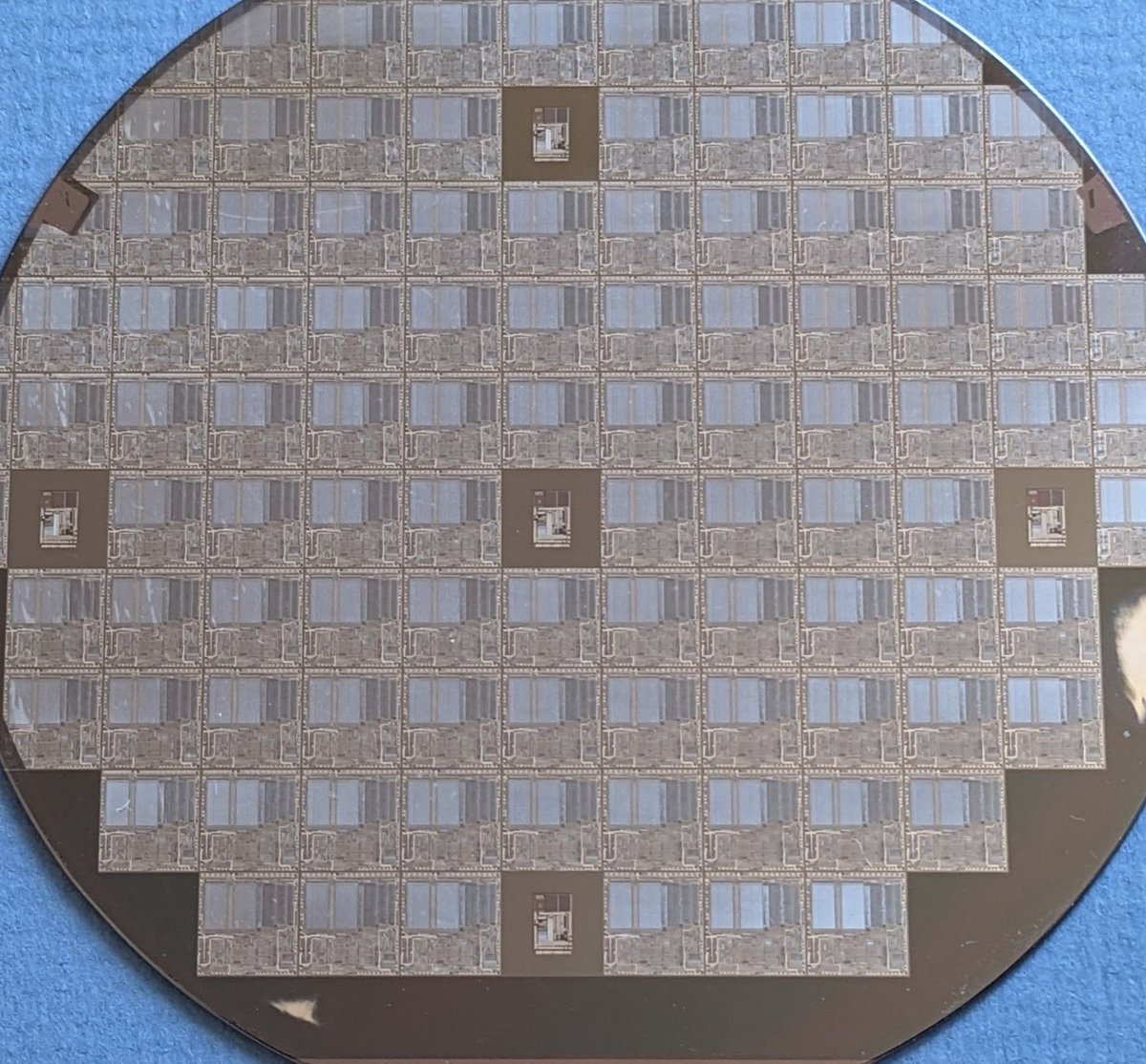

Ethernet was invented at Xerox Parc in 1973 and became the most popular way to wire computers into a network. AMD made the LANCE chip in 1982, containing most of the interface circuitry. I made a die photo of the chip. 1/11

• • •

Missing some Tweet in this thread? You can try to

force a refresh