I miss the insanity of 80s processor design.

Intel’s iAPX 432 was a “micromainframe”.

It had no general purpose registers, supported object orientation *directly*, and performed garbage collection on-chip.

It was also 23x slower than an 8086. Here's why it failed.

Intel’s iAPX 432 was a “micromainframe”.

It had no general purpose registers, supported object orientation *directly*, and performed garbage collection on-chip.

It was also 23x slower than an 8086. Here's why it failed.

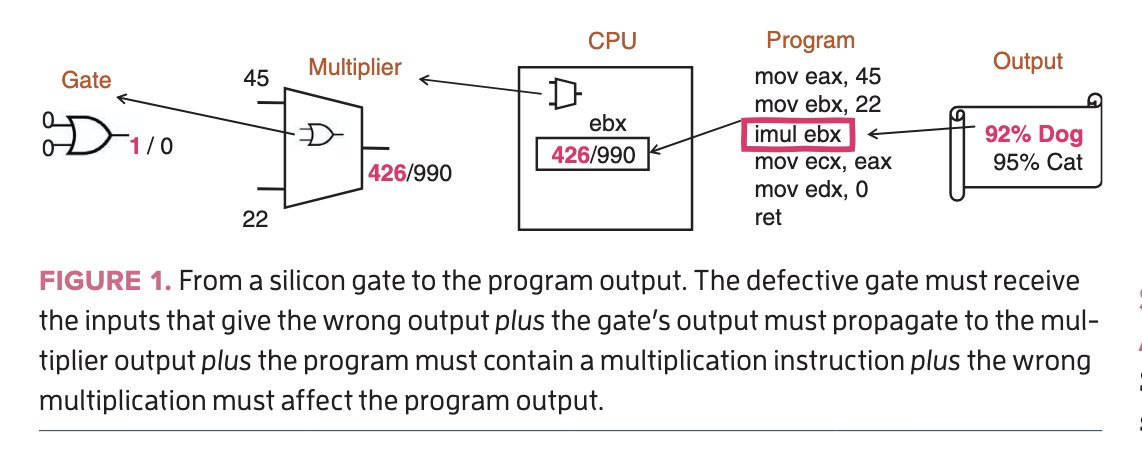

Intel targeted Ada so aggressively that C support was an afterthought.

Problem was, particularly at the time, the Ada compiler was extremely untuned and immature.

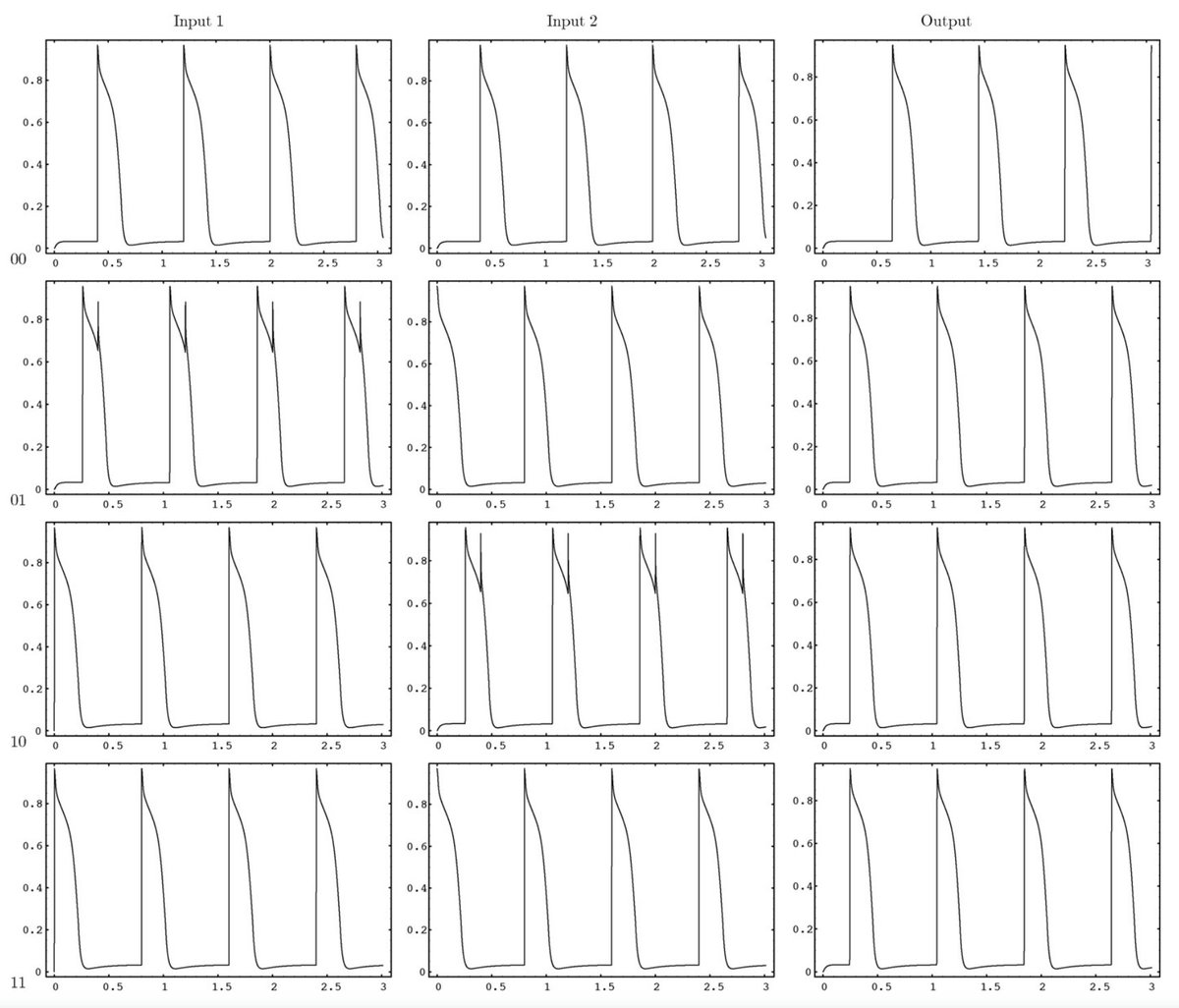

Scalar instructions were basically never used; *everything* was huge object-oriented calls.

Problem was, particularly at the time, the Ada compiler was extremely untuned and immature.

Scalar instructions were basically never used; *everything* was huge object-oriented calls.

The “micromainframe” moniker wasn’t just marketing. One I/O chip could stitch together 63 CPUs on a single bus.

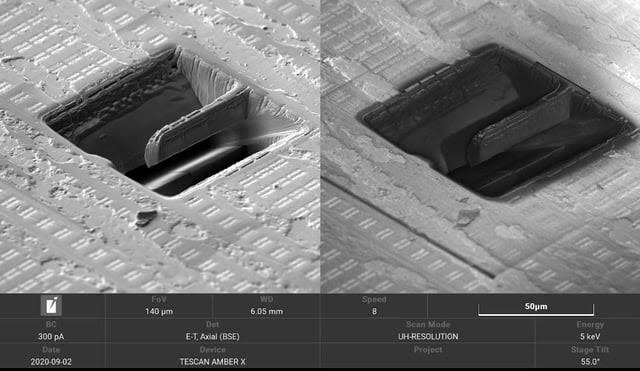

Essentially memory safe in-hardware; dangling pointers were impossible at the ISA level.

Partners like BiiN suggested using the CPU for nuclear-reactor control.

Essentially memory safe in-hardware; dangling pointers were impossible at the ISA level.

Partners like BiiN suggested using the CPU for nuclear-reactor control.

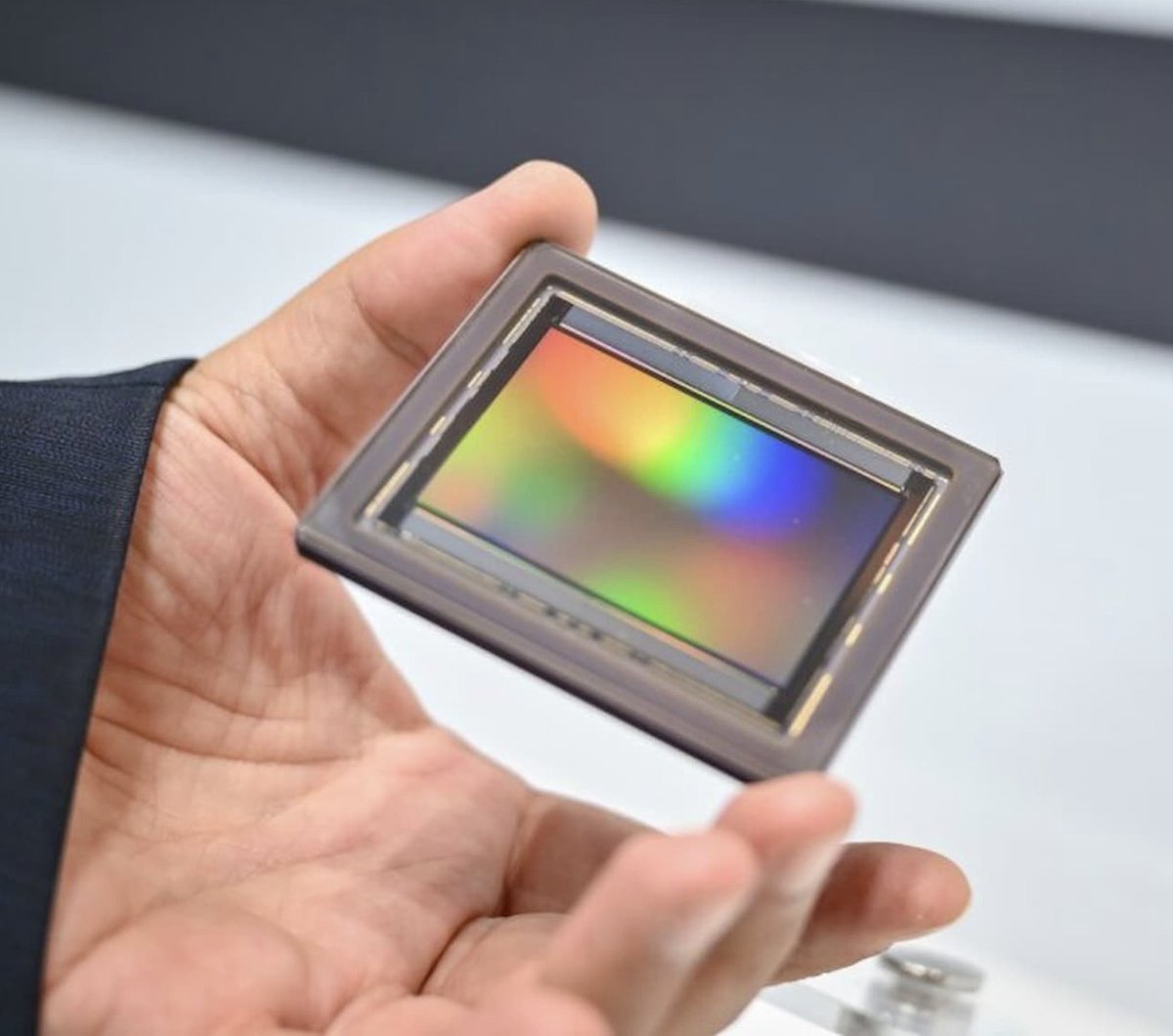

Although the iAPX 432 was a commercial flop, the design lineage was appealing to unique, military applications.

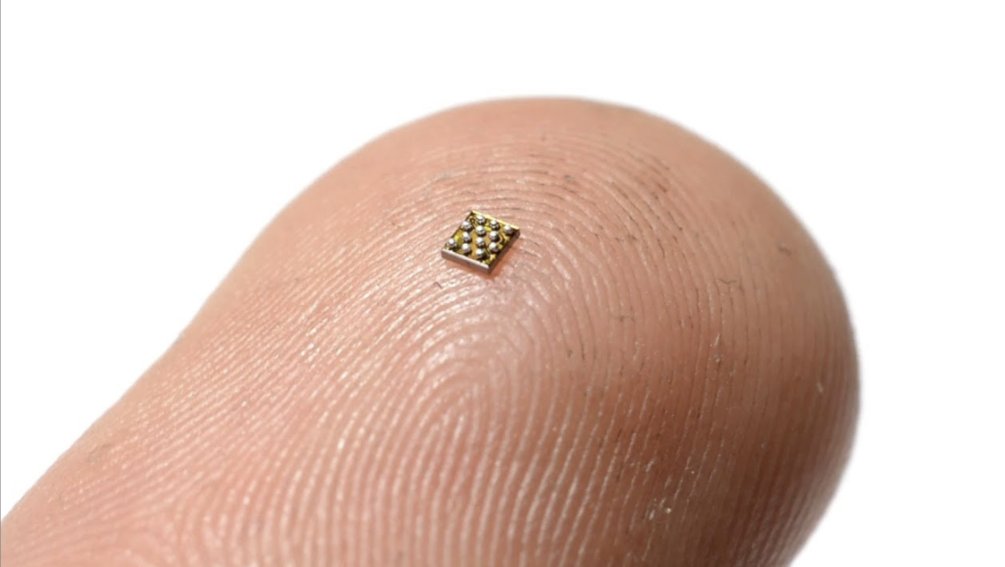

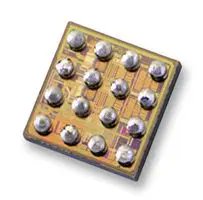

Huges Aircraft used 35 i960 MXs (a rad-hard RISC chip birthed from the 432) for the main avionics of the F22.

The equivalent of 2 Cray super-computers on a single aircraft!

If you’d like to learn more about this unique ISA, check out Ken Shirriff’s blog. He goes into great detail about the history of the i960 design, and the 432 roots:

righto.com/2023/07/the-co…

Huges Aircraft used 35 i960 MXs (a rad-hard RISC chip birthed from the 432) for the main avionics of the F22.

The equivalent of 2 Cray super-computers on a single aircraft!

If you’d like to learn more about this unique ISA, check out Ken Shirriff’s blog. He goes into great detail about the history of the i960 design, and the 432 roots:

righto.com/2023/07/the-co…

• • •

Missing some Tweet in this thread? You can try to

force a refresh