How to get URL link on X (Twitter) App

Awkward pause, but a few things got me thinking, and I checked a few things.

Awkward pause, but a few things got me thinking, and I checked a few things.

Alder Lake-S is the first consumer chip which brought PCIe 5 support and it's always interesting to see how a new standard looks on a die shot.

Alder Lake-S is the first consumer chip which brought PCIe 5 support and it's always interesting to see how a new standard looks on a die shot.

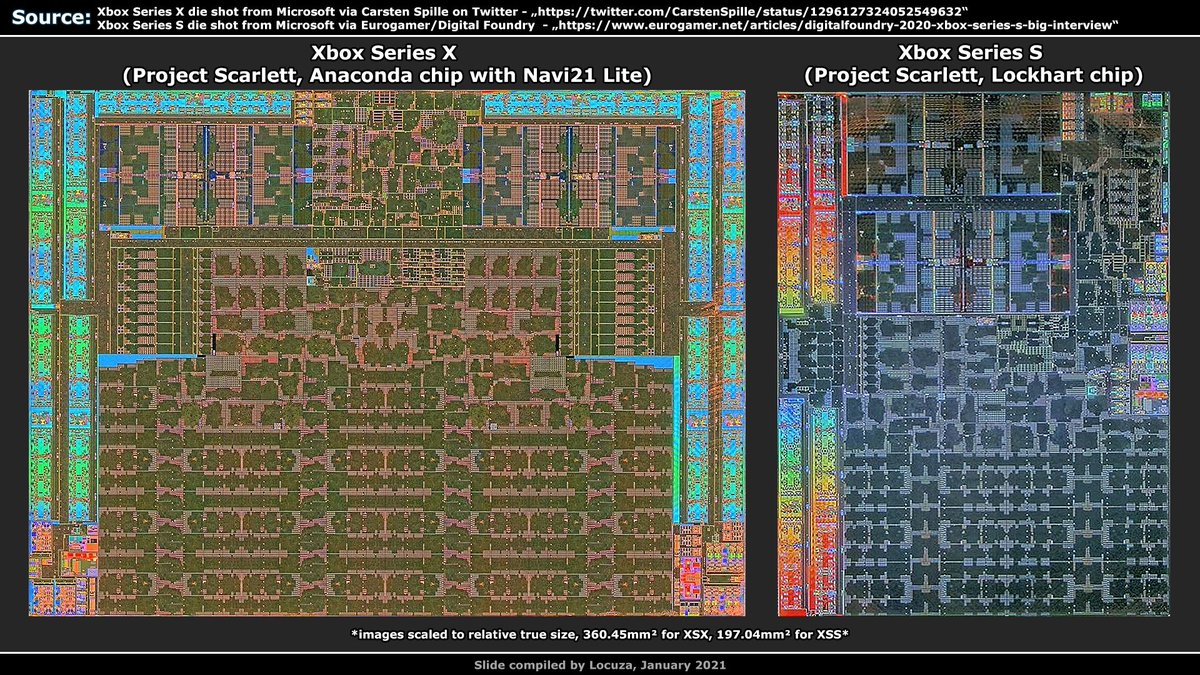

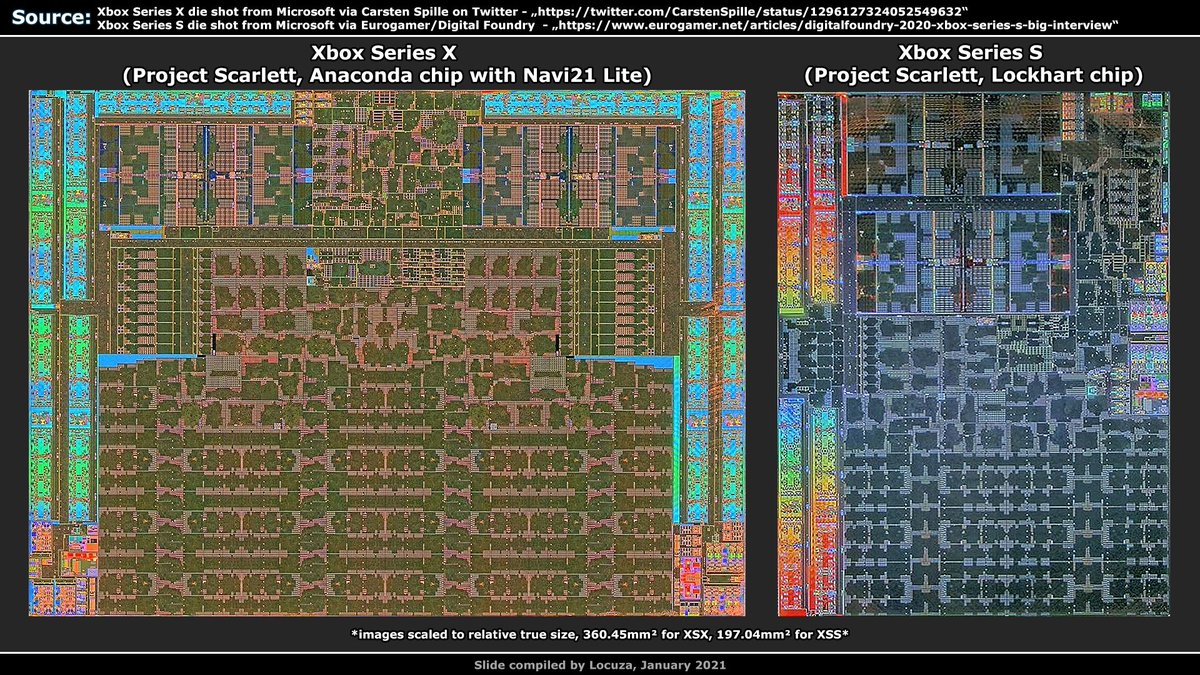

https://twitter.com/locuza_/status/1361026970893627398

It was premature from me to claim that Sony likely cut the FP pipes from 256b to 128b based on totally dark rectangles.

It was premature from me to claim that Sony likely cut the FP pipes from 256b to 128b based on totally dark rectangles.

The custom FPU is now quite a bit shorter, aligning with the µcode ROM block.

The custom FPU is now quite a bit shorter, aligning with the µcode ROM block.

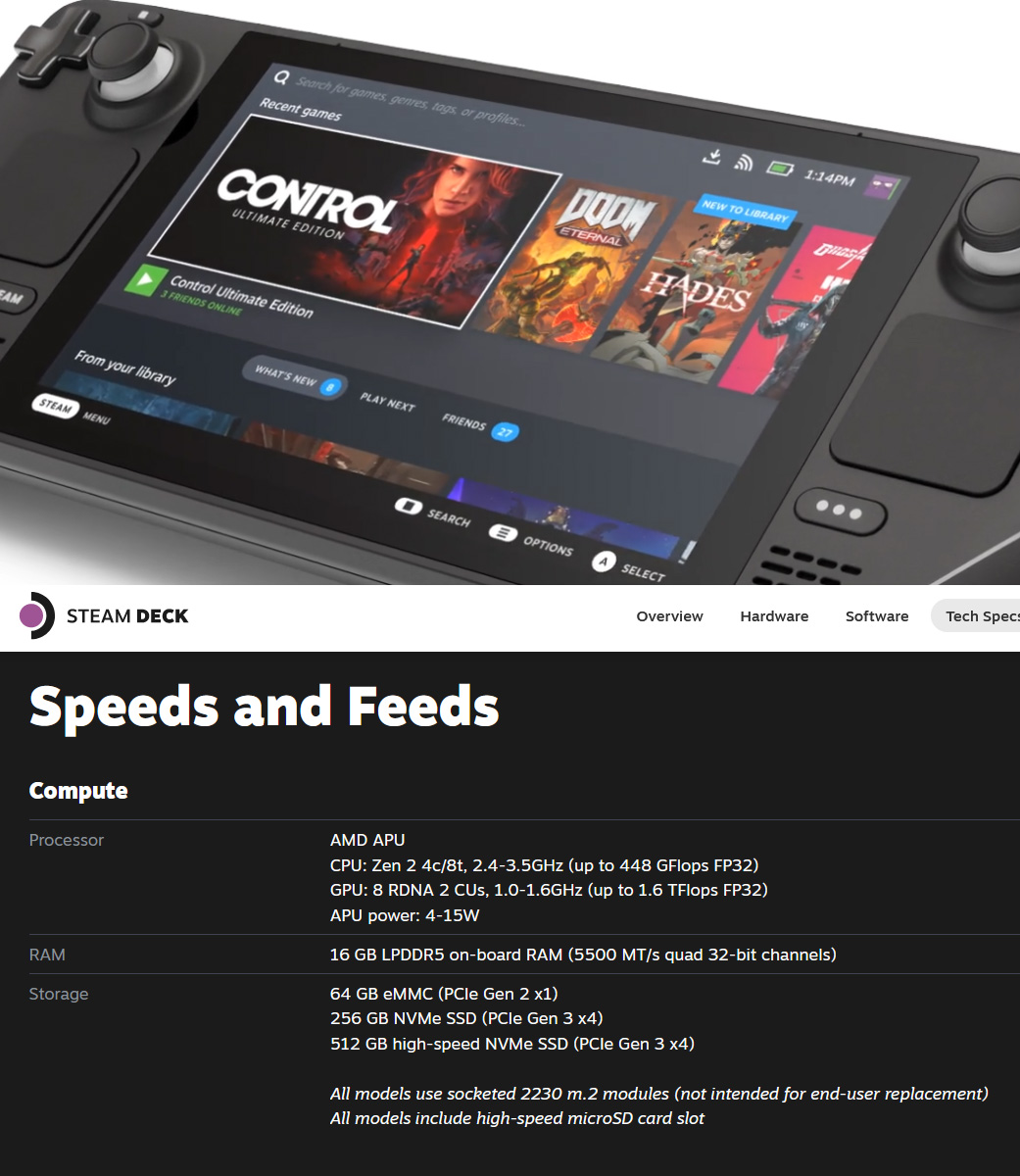

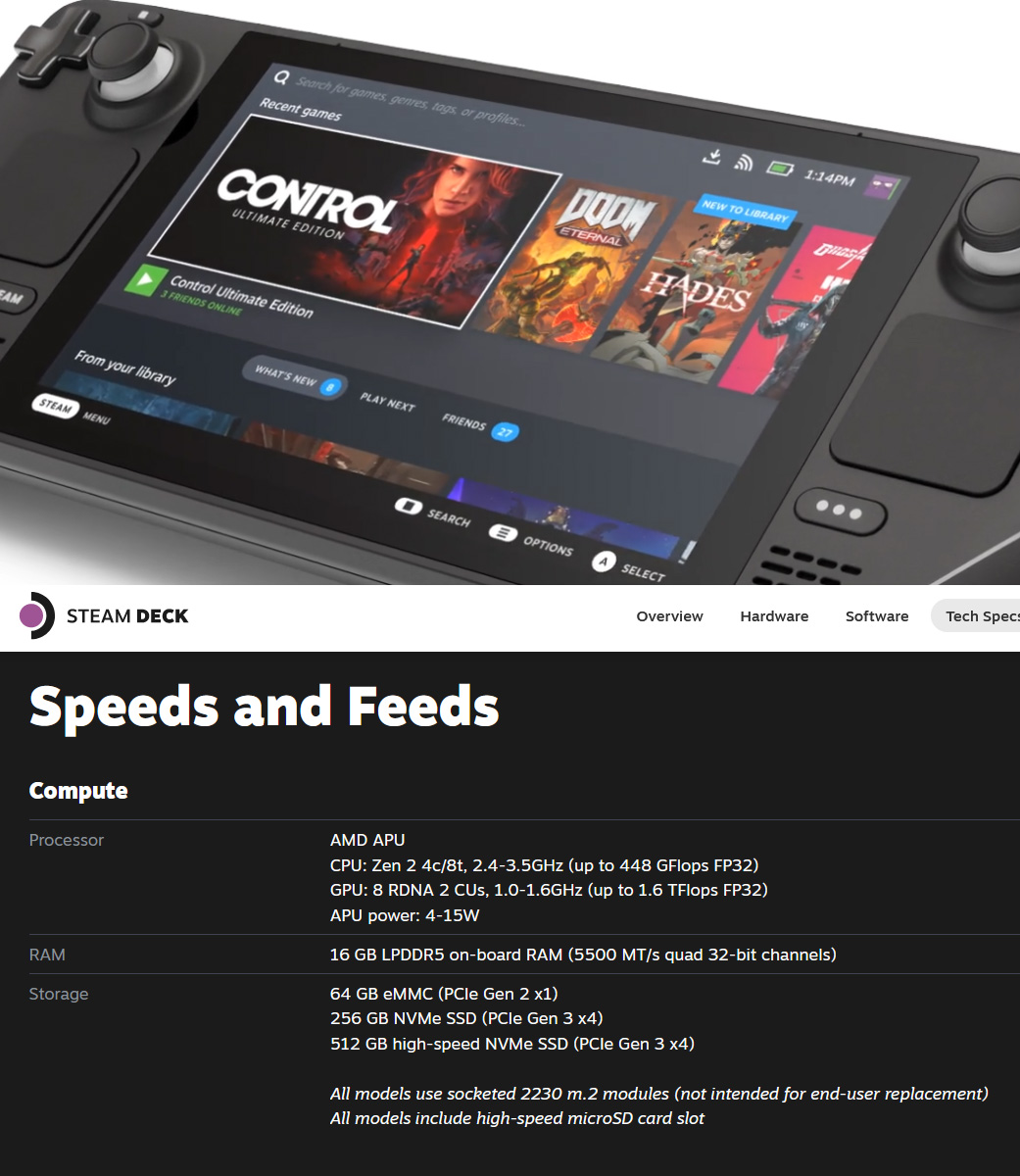

Valve claims now 4x 32-Bit (128-Bit) which fits to 4 UMCs.

Valve claims now 4x 32-Bit (128-Bit) which fits to 4 UMCs.

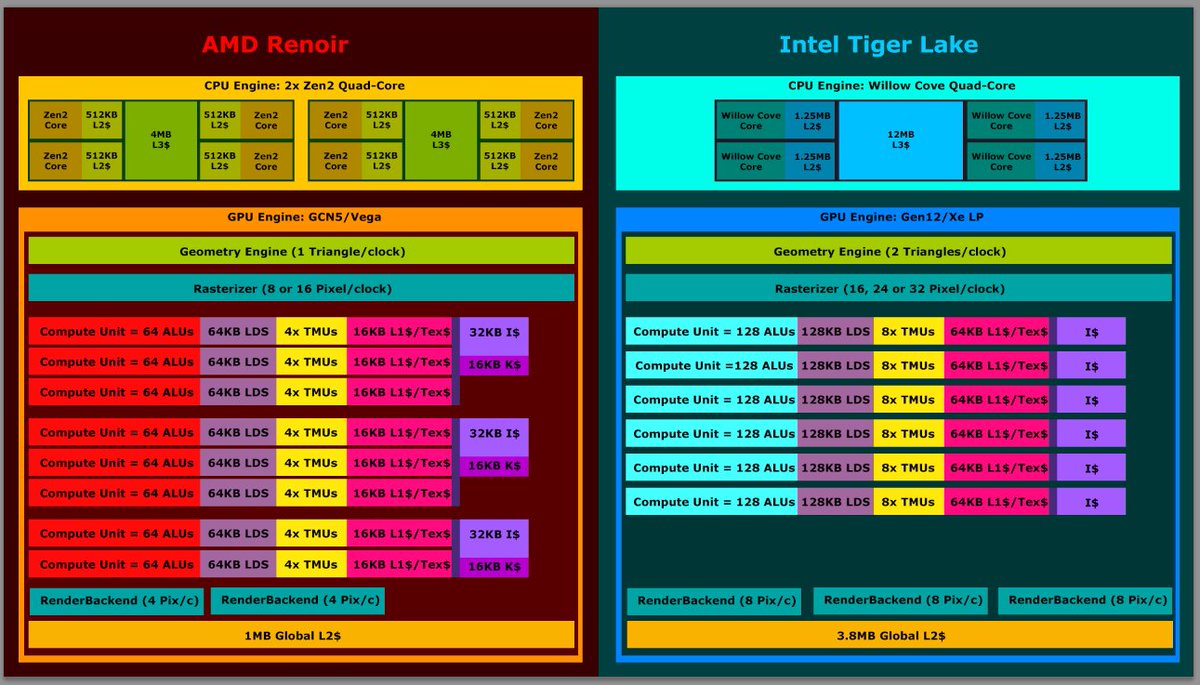

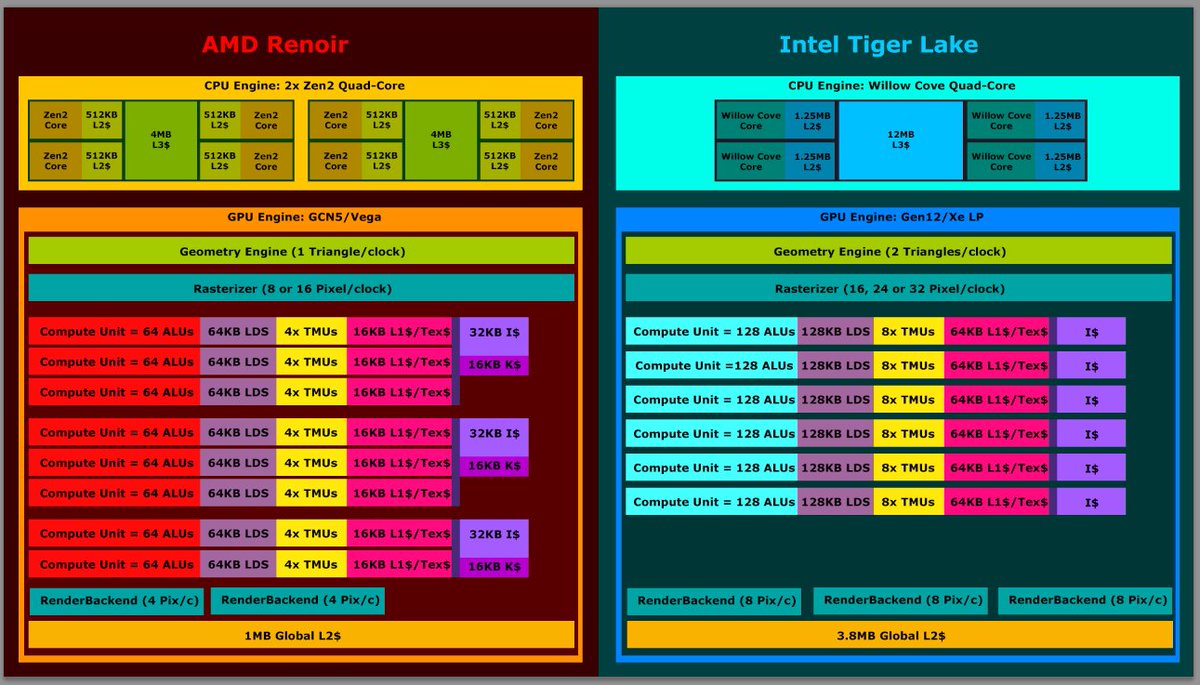

I really like the CPU engine from Intel.

I really like the CPU engine from Intel.

The specs with 5248 "CUDA cores" are already out there for the GTX3090.

The specs with 5248 "CUDA cores" are already out there for the GTX3090.