How to get URL link on X (Twitter) App

The site has two key sections: Section A and Section B.

The site has two key sections: Section A and Section B.

For people outside packaging, here is the intuitive way to think about it. Chips do not move through OSAT as loose magical objects. They move through a very physical factory flow with trays, boats, carriers, sockets, test handlers, ovens, lid attach, mark, inspection, and shipping constraints. There are standard footprints for how packaged parts are handled. A common JEDEC tray is roughly 12.7 by 5.35 inches (322.6 × 135.9 cm) externally, and once your package starts eating too much of that real estate, everything gets uglier. Fewer units per tray. Worse mechanical margin. Harder handling. More custom tooling. More risk in test and burn-in. Higher cost everywhere. (2/5)

For people outside packaging, here is the intuitive way to think about it. Chips do not move through OSAT as loose magical objects. They move through a very physical factory flow with trays, boats, carriers, sockets, test handlers, ovens, lid attach, mark, inspection, and shipping constraints. There are standard footprints for how packaged parts are handled. A common JEDEC tray is roughly 12.7 by 5.35 inches (322.6 × 135.9 cm) externally, and once your package starts eating too much of that real estate, everything gets uglier. Fewer units per tray. Worse mechanical margin. Harder handling. More custom tooling. More risk in test and burn-in. Higher cost everywhere. (2/5)

What's driving it:

What's driving it:

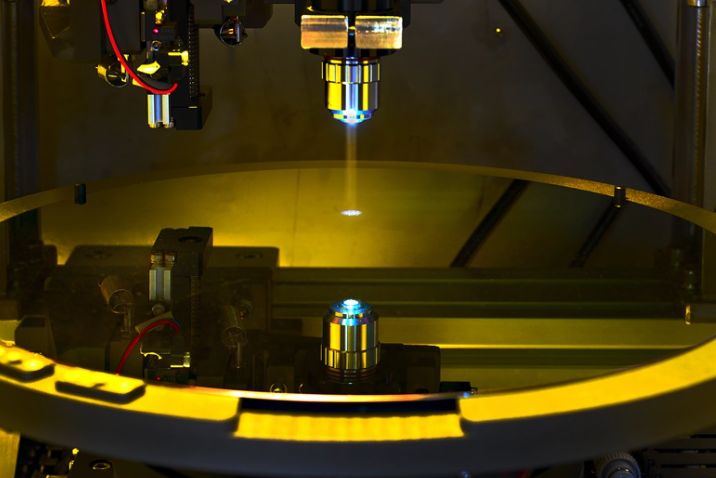

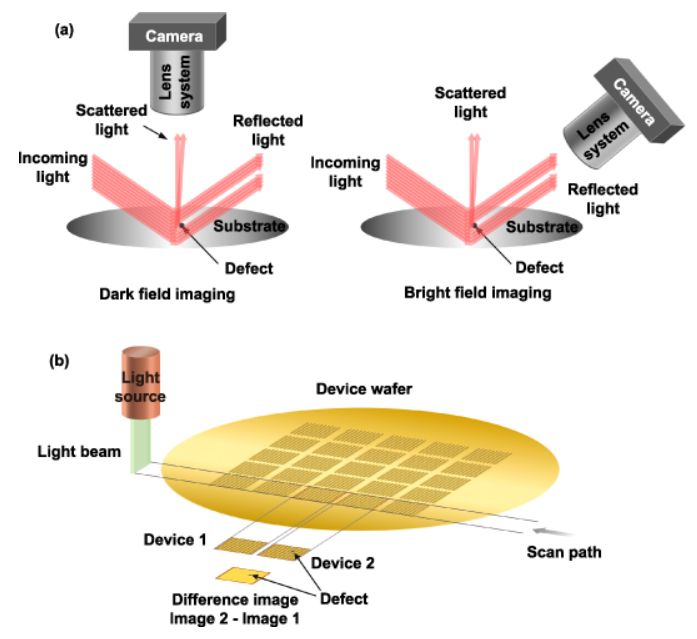

Phase 1 — Wafer-Level Single-Die Test: The EIC and PIC are tested separately at the wafer level before bonding. The EIC is standard CMOS wafer sort (no new equipment). The PIC requires novel double-sided electro-optical probing — this is where all the new equipment spend goes. (2/5)

Phase 1 — Wafer-Level Single-Die Test: The EIC and PIC are tested separately at the wafer level before bonding. The EIC is standard CMOS wafer sort (no new equipment). The PIC requires novel double-sided electro-optical probing — this is where all the new equipment spend goes. (2/5)

It's 1916. Czochralski, a Polish chemist, is focused on understanding how metals crystallize. Labs back then were often cluttered, intense places with random objects and inventions scattered around.

It's 1916. Czochralski, a Polish chemist, is focused on understanding how metals crystallize. Labs back then were often cluttered, intense places with random objects and inventions scattered around.

The project has already taken an absurd 1200 days between announcement and groundbreaking. Competitors overseas who began at the same time now have built and working fabs. (2/10)

The project has already taken an absurd 1200 days between announcement and groundbreaking. Competitors overseas who began at the same time now have built and working fabs. (2/10)

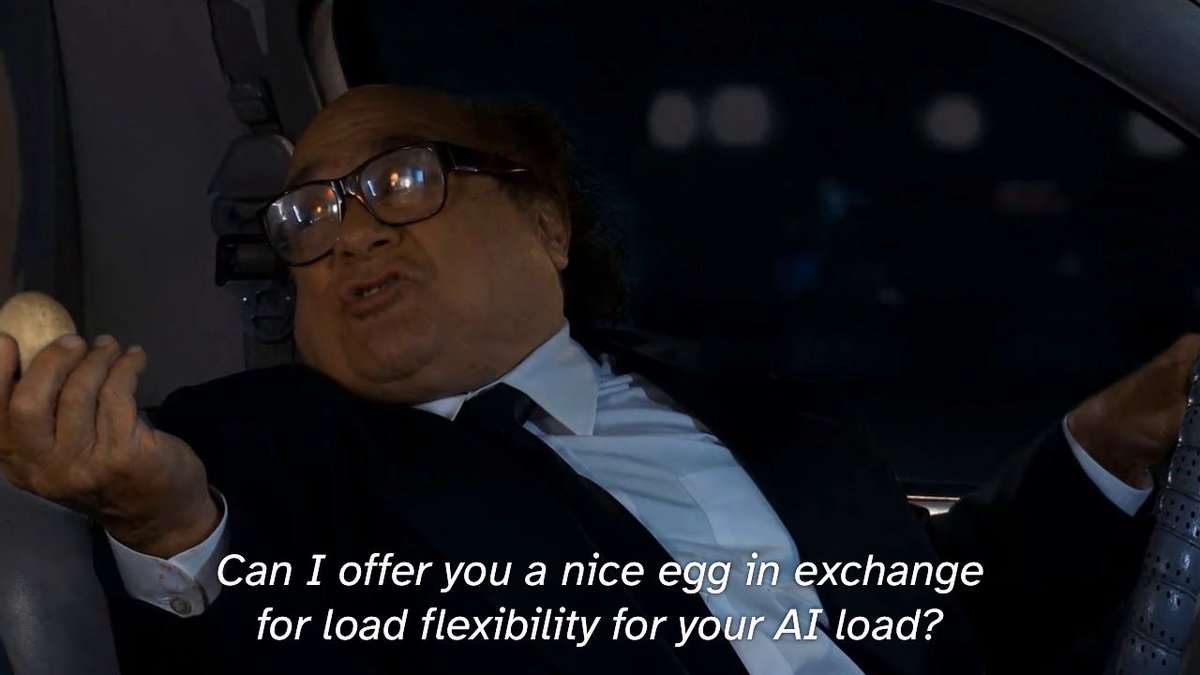

Let's use rule-of-thumb figures: AI clusters make $12M/MW annually in revenue, and have an EBIT margin of around 20%.

Let's use rule-of-thumb figures: AI clusters make $12M/MW annually in revenue, and have an EBIT margin of around 20%.

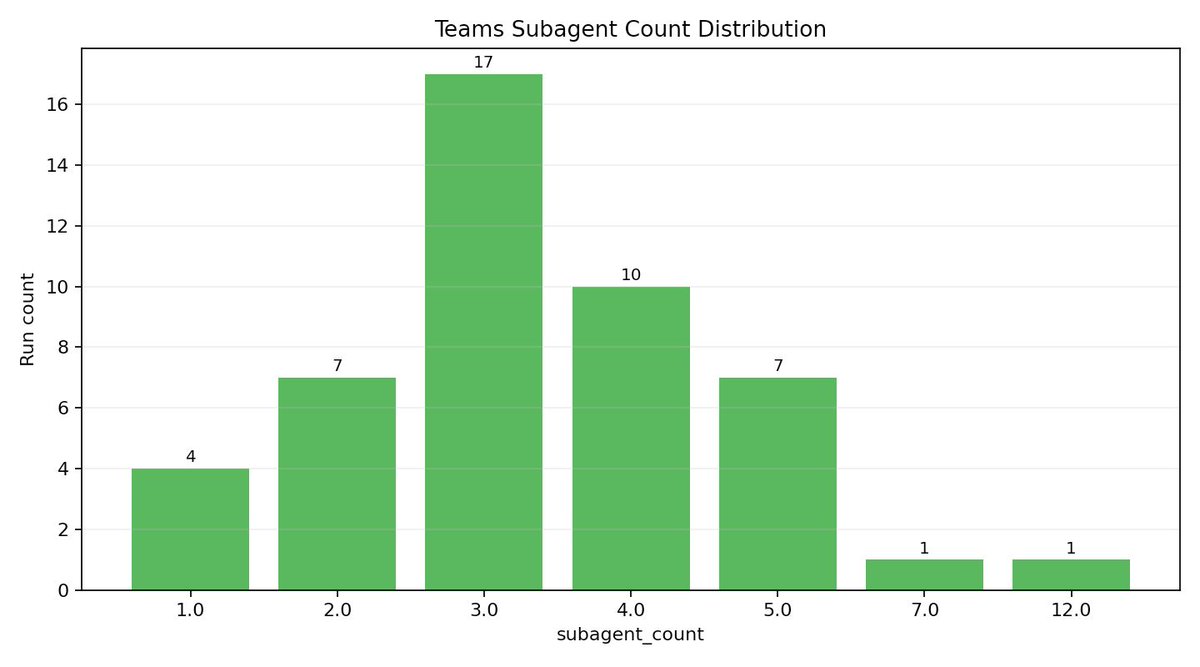

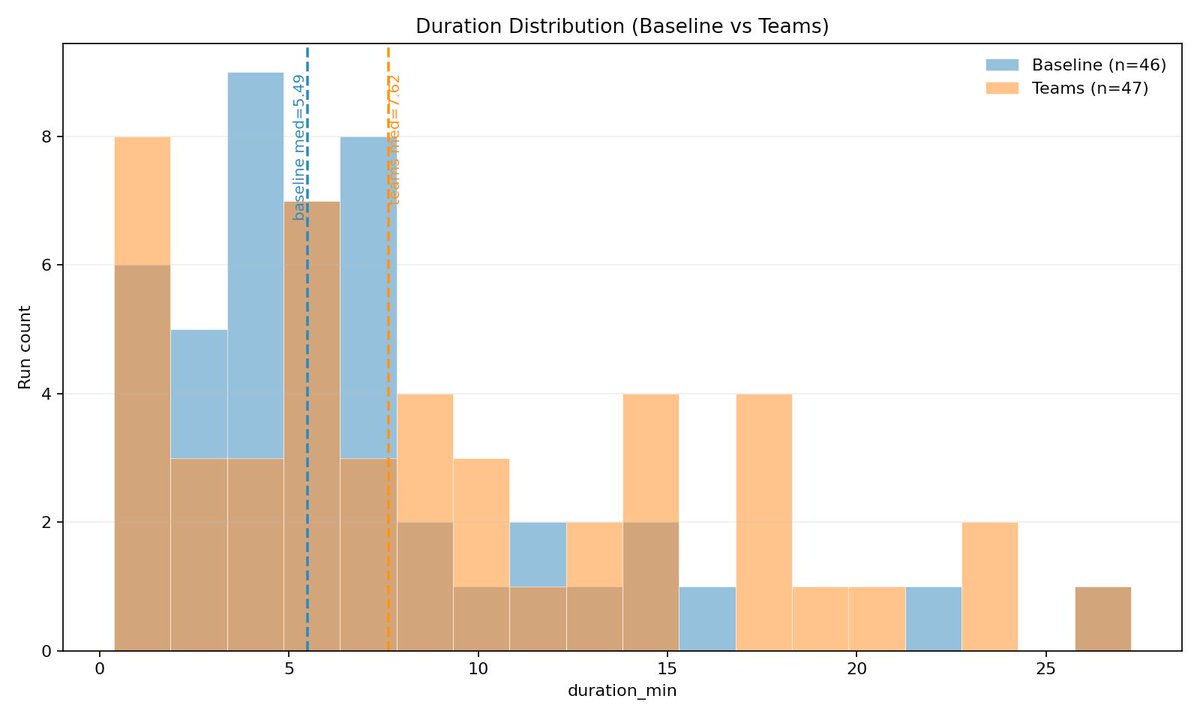

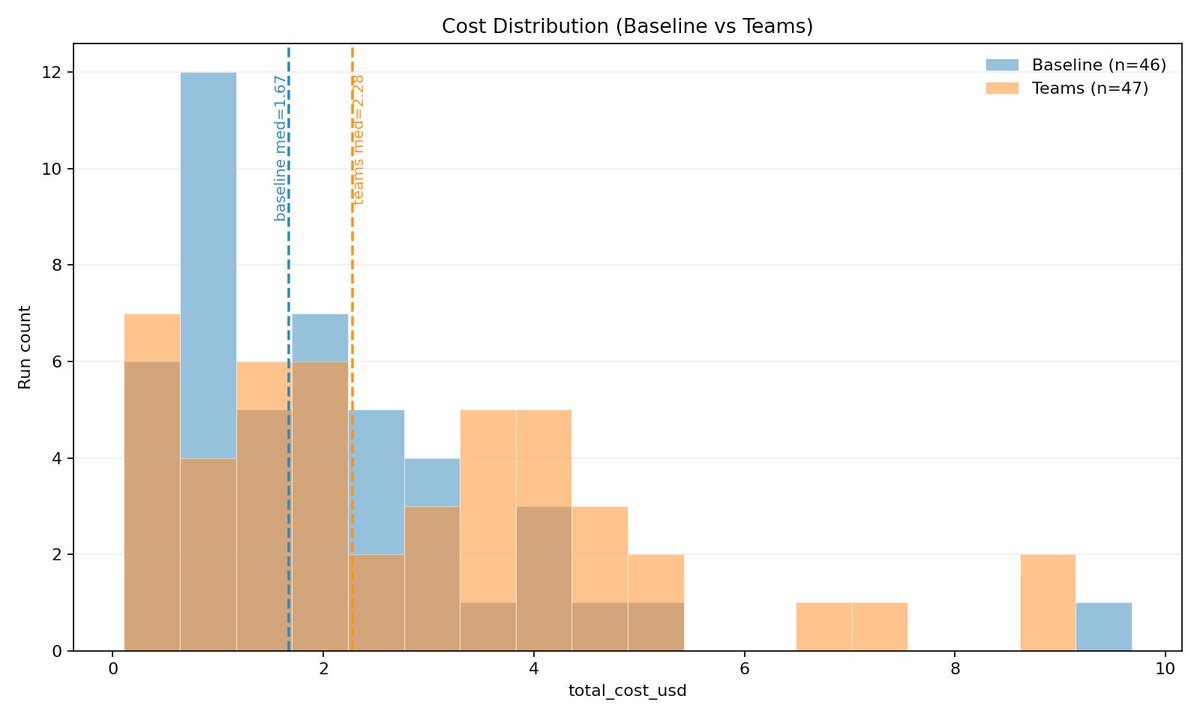

We ran a small benchmark with WideSearch on Claude Teams: 30 unique English tasks, 2 trials each, 30-min timeout, GPT-5.2 judge. We compare it to a Opus 4.6 baseline.

We ran a small benchmark with WideSearch on Claude Teams: 30 unique English tasks, 2 trials each, 30-min timeout, GPT-5.2 judge. We compare it to a Opus 4.6 baseline.

A fully loaded AI rack can weigh up to 3,700 lbs. That’s the weight of a Ford Explorer concentrated into a 2x4 foot footprint. Standard pallets would crush instantly. These AI racks require custom-engineered reinforced bases with shock-absorbent foam just to keep them from tearing through the floor. (2/9)

A fully loaded AI rack can weigh up to 3,700 lbs. That’s the weight of a Ford Explorer concentrated into a 2x4 foot footprint. Standard pallets would crush instantly. These AI racks require custom-engineered reinforced bases with shock-absorbent foam just to keep them from tearing through the floor. (2/9)

Although these two terms are often discussed together, they actually refer to two distinct domains.

Although these two terms are often discussed together, they actually refer to two distinct domains.

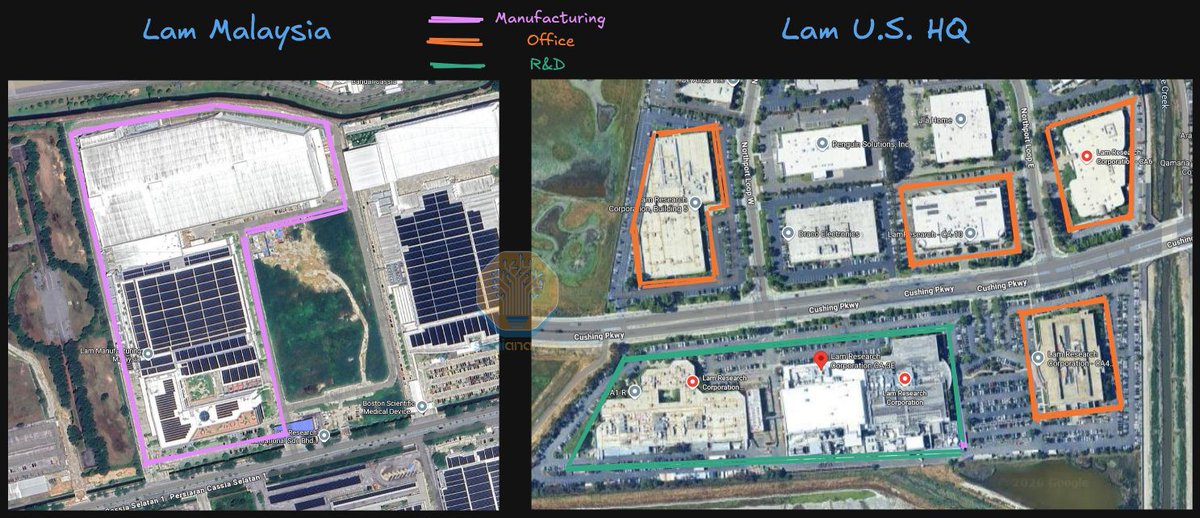

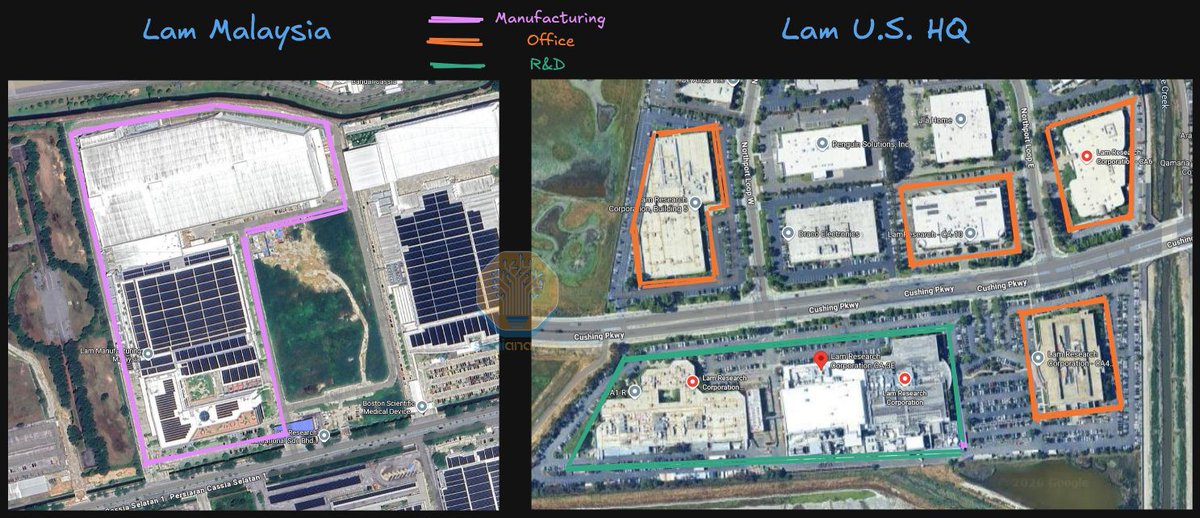

In 2022 we flagged Lam Research expanding in Malaysia. Today, most of its high-volume production is there, not the U.S. That trend has only accelerated. (2/6) newsletter.semianalysis.com/p/lam-research…

In 2022 we flagged Lam Research expanding in Malaysia. Today, most of its high-volume production is there, not the U.S. That trend has only accelerated. (2/6) newsletter.semianalysis.com/p/lam-research…

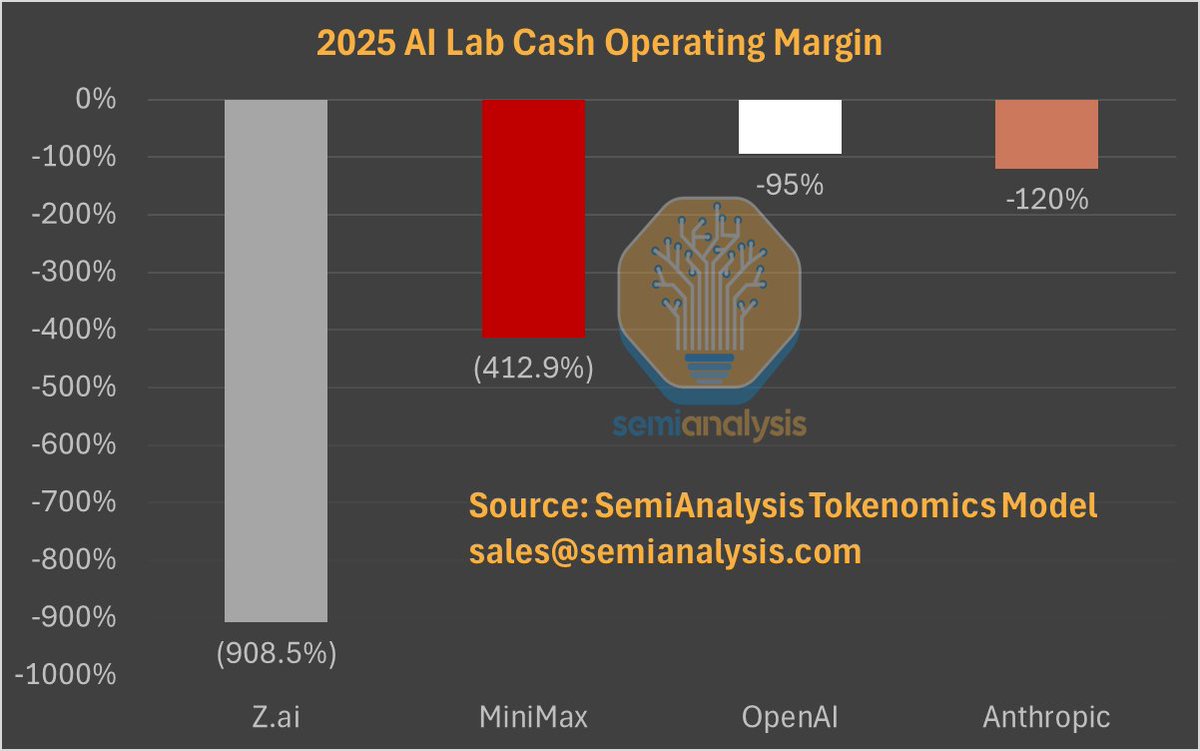

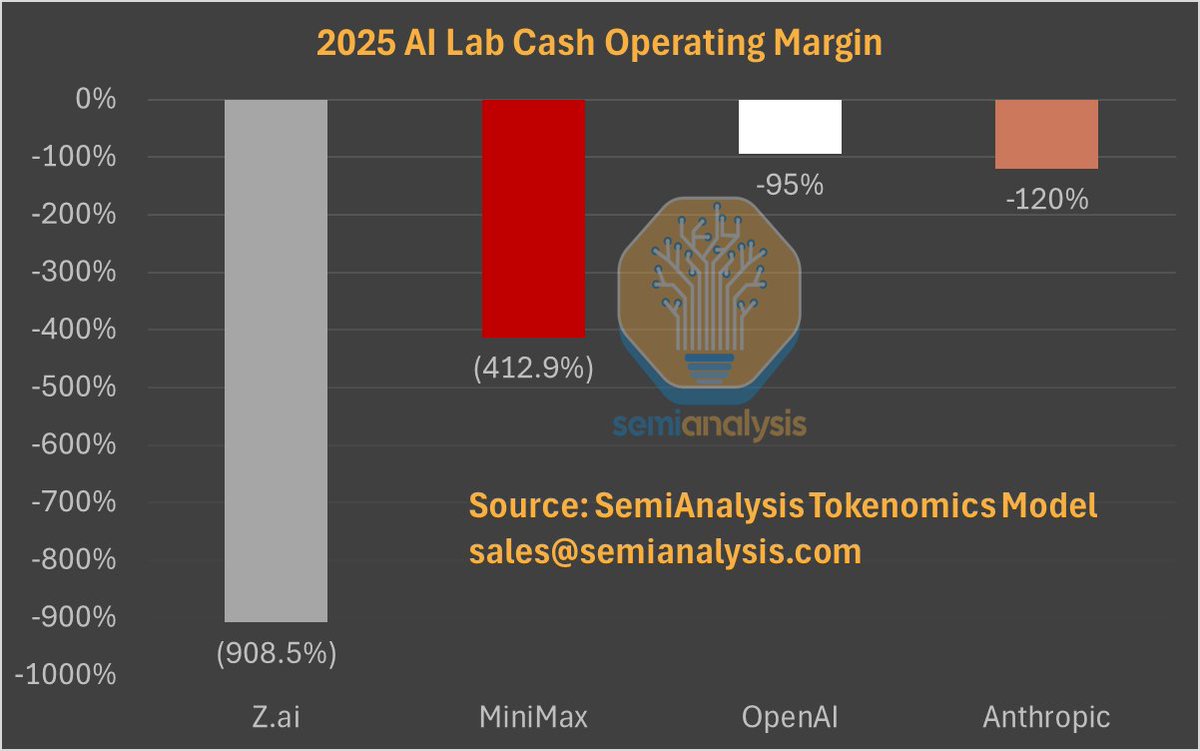

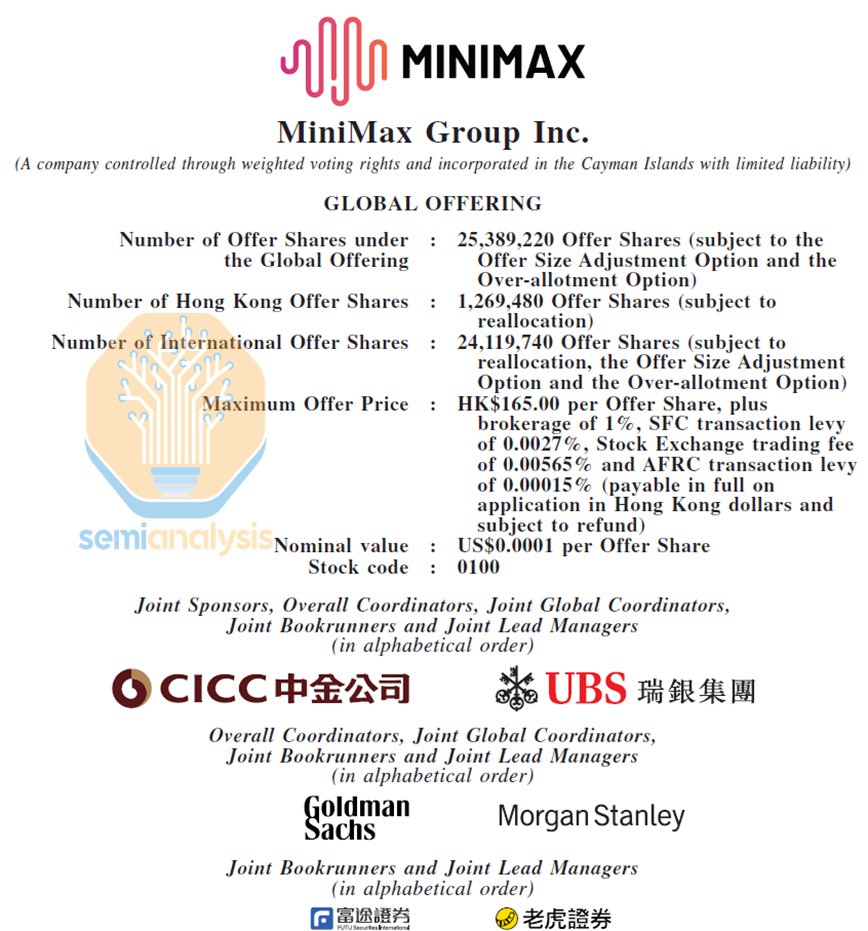

MiniMax (0100 HK) and aka Knowledge Atlas fka ZhiPu (2513 HK) both give a glimpse into the economics of an AI Lab, demonstrating strong product momentum as well as a flagrant disregard for profitability. (2/5) 🔥📉Z.ai

MiniMax (0100 HK) and aka Knowledge Atlas fka ZhiPu (2513 HK) both give a glimpse into the economics of an AI Lab, demonstrating strong product momentum as well as a flagrant disregard for profitability. (2/5) 🔥📉Z.ai

A recip is more modular than turbines, happier at partial loads, and more comprehensible to maintain. You're mostly changing lubricants, whereas a turbine requires no maintenance...until it needs a massive overhaul. (2/4)

A recip is more modular than turbines, happier at partial loads, and more comprehensible to maintain. You're mostly changing lubricants, whereas a turbine requires no maintenance...until it needs a massive overhaul. (2/4)

Back in the '90s, parts of the American electric grid were "deregulating." These reforms gave us commodity markets for electricity--aka ISOs and RTOs. INDEPENDENT POWER PRODUCERS (IPPs), often utilities from other states, could build and run their own power plants and make money on these new electricity markets. Their generator of choice? The COMBINED CYCLE GAS PLANT (CCGT), particularly the then-new F-CLASS. (2/8)

Back in the '90s, parts of the American electric grid were "deregulating." These reforms gave us commodity markets for electricity--aka ISOs and RTOs. INDEPENDENT POWER PRODUCERS (IPPs), often utilities from other states, could build and run their own power plants and make money on these new electricity markets. Their generator of choice? The COMBINED CYCLE GAS PLANT (CCGT), particularly the then-new F-CLASS. (2/8)

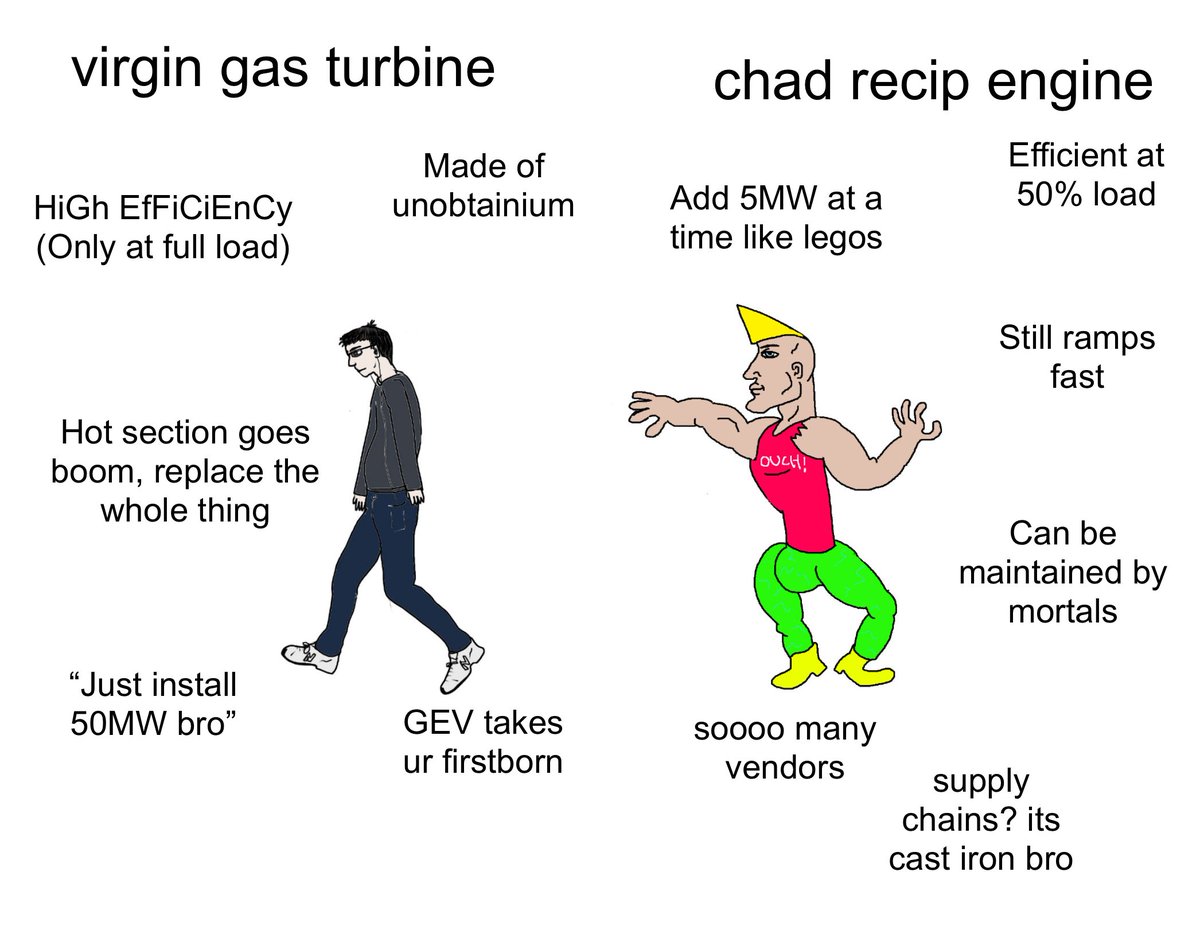

Before the 1970s, doping was performed through thermal diffusion in high-temperature furnaces.

Before the 1970s, doping was performed through thermal diffusion in high-temperature furnaces.

Both have increased their investments to capture more revenue in consumer, networking, industrial and computing markets. Non-smartphones account for 30% of Qualcomm's semiconductor revenue and 48% of MediaTek's. Qualcomm has a target of $22B non-smartphone chip revenue by FY29 at a 5-year CAGR of 21%. Qualcomm built a strong moat in autos but made mixed progress in IoT (a collection of end markets including PC, consumer, networking and infrastructure). (2/7)

Both have increased their investments to capture more revenue in consumer, networking, industrial and computing markets. Non-smartphones account for 30% of Qualcomm's semiconductor revenue and 48% of MediaTek's. Qualcomm has a target of $22B non-smartphone chip revenue by FY29 at a 5-year CAGR of 21%. Qualcomm built a strong moat in autos but made mixed progress in IoT (a collection of end markets including PC, consumer, networking and infrastructure). (2/7)

To solve this problem, Meta turned to the use of Disaggregated Scheduled Fabrics (DSFs). Being “Scheduled” means that a credit-based system is used to control flows and prevent congestion – before a node can send packets across the network, it must first send a credit request towards the receiving node to make sure that the receiving end has enough buffer to receive the packet. These packets also travel over a fabric that cellifies the packets, breaking it into smaller cells and spreading it across multiple routes in the fabric. (2/6)

To solve this problem, Meta turned to the use of Disaggregated Scheduled Fabrics (DSFs). Being “Scheduled” means that a credit-based system is used to control flows and prevent congestion – before a node can send packets across the network, it must first send a credit request towards the receiving node to make sure that the receiving end has enough buffer to receive the packet. These packets also travel over a fabric that cellifies the packets, breaking it into smaller cells and spreading it across multiple routes in the fabric. (2/6)