How to get URL link on X (Twitter) App

From the proposed method it was achieved record subthreshold slope (<75mv/dec) and drain current (Idmax>900 µA/µm at <50nm gate length) in sub-1nm-thick monolayer MoS2 GAA NMOS transistors.

From the proposed method it was achieved record subthreshold slope (<75mv/dec) and drain current (Idmax>900 µA/µm at <50nm gate length) in sub-1nm-thick monolayer MoS2 GAA NMOS transistors.

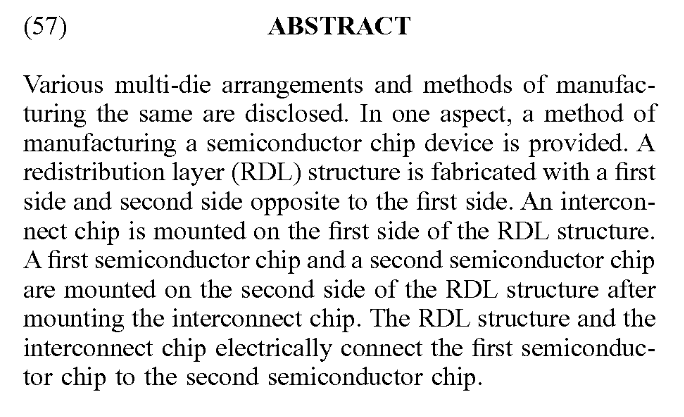

Upon analyzing it, I was absolutely shocked by what I saw and was certain that this patent would never be granted in the state in which it was presented. However, yesterday I received notification that this patent had been granted.

Upon analyzing it, I was absolutely shocked by what I saw and was certain that this patent would never be granted in the state in which it was presented. However, yesterday I received notification that this patent had been granted.

By reverse-engineering the ip-stride prefetcher in modern intel processors, the researchers have successfully developed three variants of AfterImage to leak control flow information across code regions, processes and the user-kernel boundary.

By reverse-engineering the ip-stride prefetcher in modern intel processors, the researchers have successfully developed three variants of AfterImage to leak control flow information across code regions, processes and the user-kernel boundary.

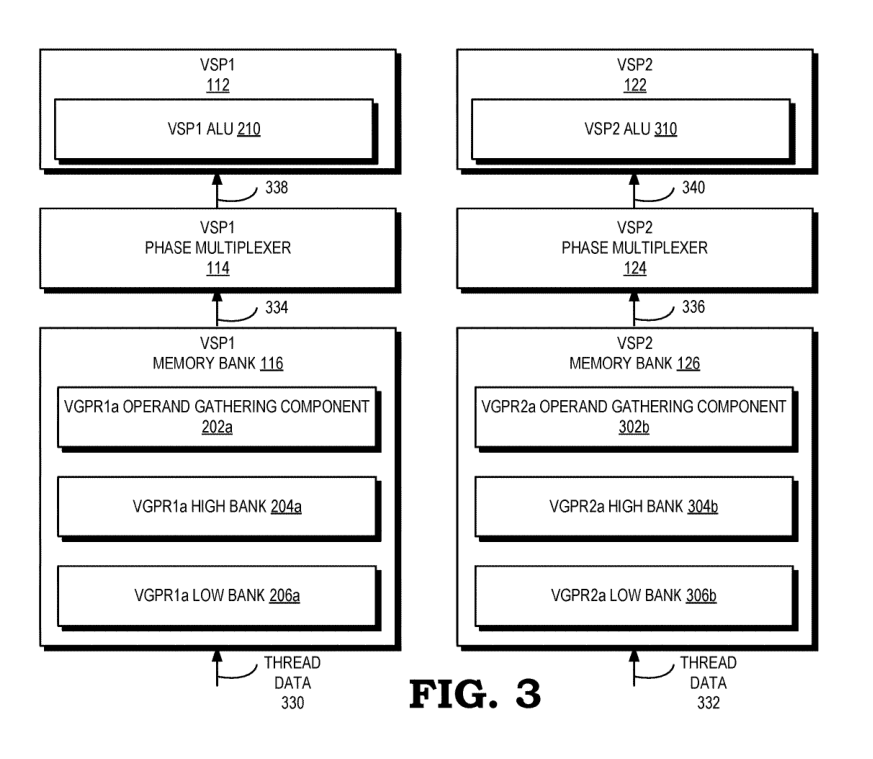

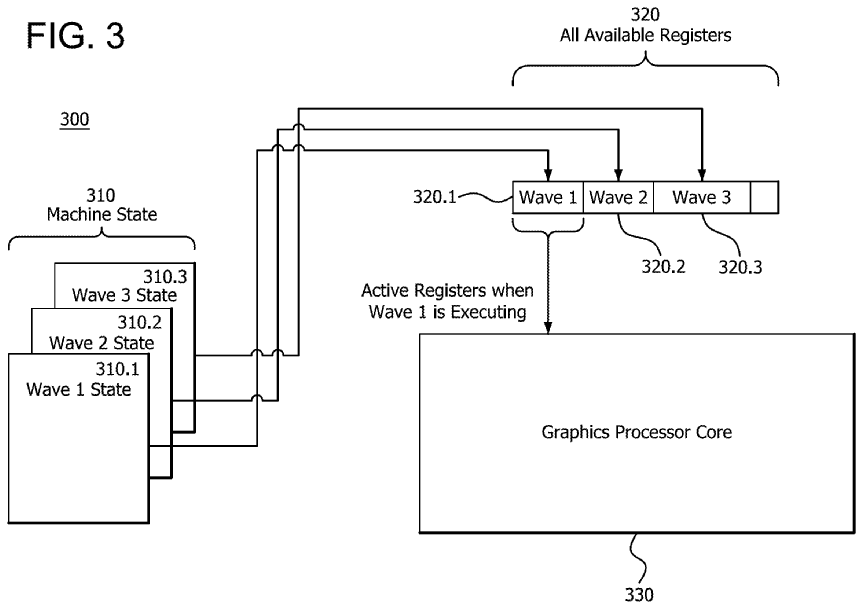

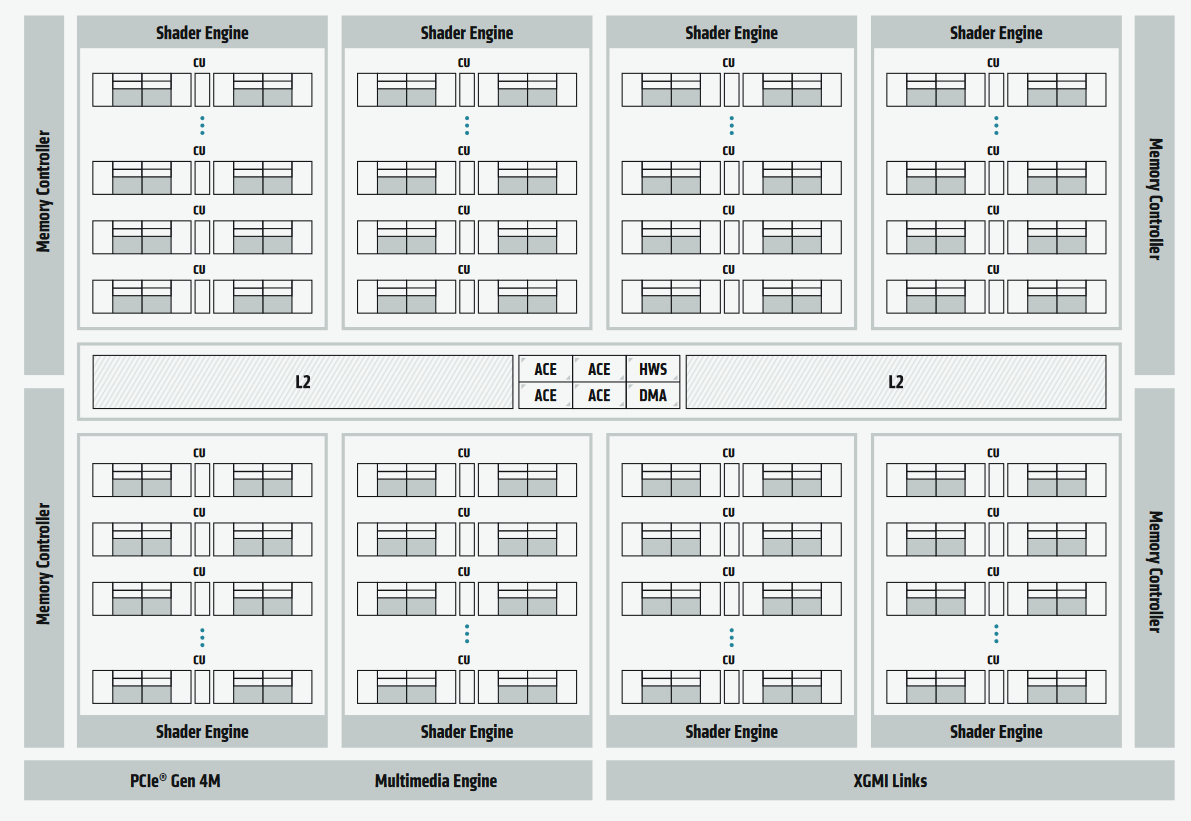

Patent: Dedicated Vector Sub-processor System - AMD

Patent: Dedicated Vector Sub-processor System - AMD

The experimental results show that CM applications from different domains outperform the best-known SIMT-based OpenCL implementations, achieving up to 2.7x speedup on the latest Intel GPU.

The experimental results show that CM applications from different domains outperform the best-known SIMT-based OpenCL implementations, achieving up to 2.7x speedup on the latest Intel GPU.

Patent: Variation-aware qubit movement scheme for noise intermediate scale quantum era computers - AMD

Patent: Variation-aware qubit movement scheme for noise intermediate scale quantum era computers - AMD

PyTorch-Direct presents a new class of tensor called “unified tensor.” While a unified tensor resides in host memory, its elements can be accessed directly by the GPUs, as if they reside in GPU memory.

PyTorch-Direct presents a new class of tensor called “unified tensor.” While a unified tensor resides in host memory, its elements can be accessed directly by the GPUs, as if they reside in GPU memory.

Also, it's proposed a neural network called ADAPTNET which recommends an array configuration and dataflow for the current layer parameters.

Also, it's proposed a neural network called ADAPTNET which recommends an array configuration and dataflow for the current layer parameters.

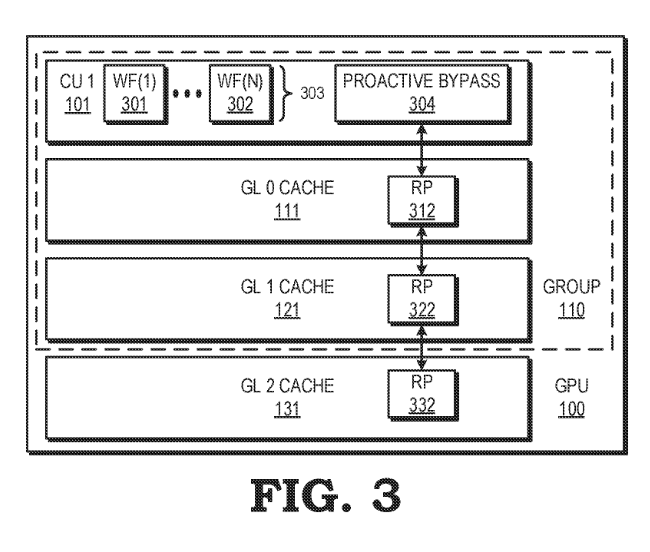

Patent: GPU cache management based on locality type detection - AMD

Patent: GPU cache management based on locality type detection - AMD

Patent: Dynamically structured single instruction, multiple data (SIMD) instructions - Xilinx

Patent: Dynamically structured single instruction, multiple data (SIMD) instructions - Xilinx

https://twitter.com/Underfox3/status/1328743554437447682

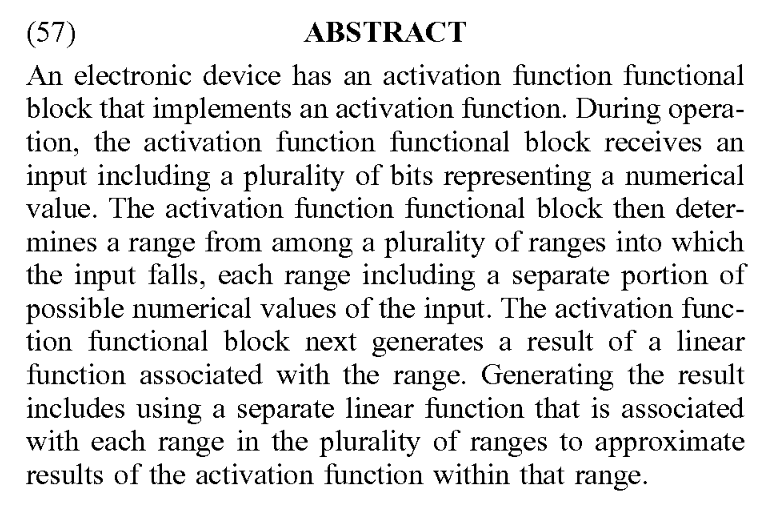

Patent: Activation Function Functional Block for Electronic Devices - AMD

Patent: Activation Function Functional Block for Electronic Devices - AMD

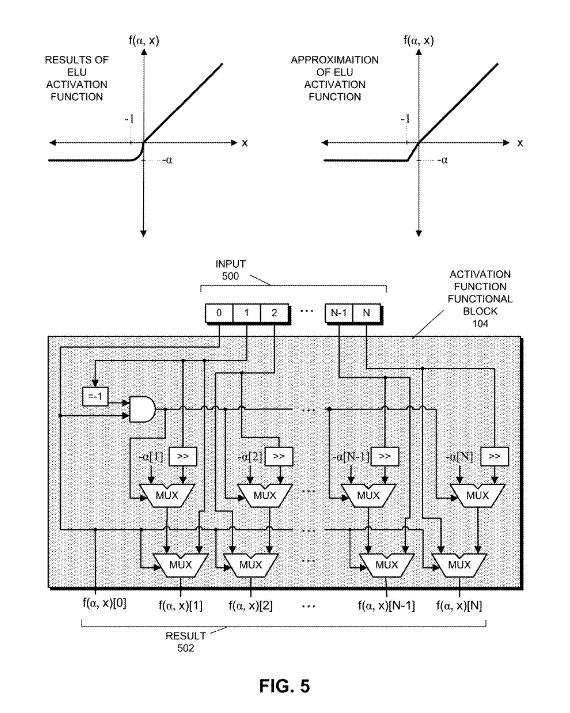

Patent: System and method for scheduling instructions in a multithread simd architecture with a fixed number of registers - AMD

Patent: System and method for scheduling instructions in a multithread simd architecture with a fixed number of registers - AMD

Patent: Side information for video data transmission - AMD

Patent: Side information for video data transmission - AMD

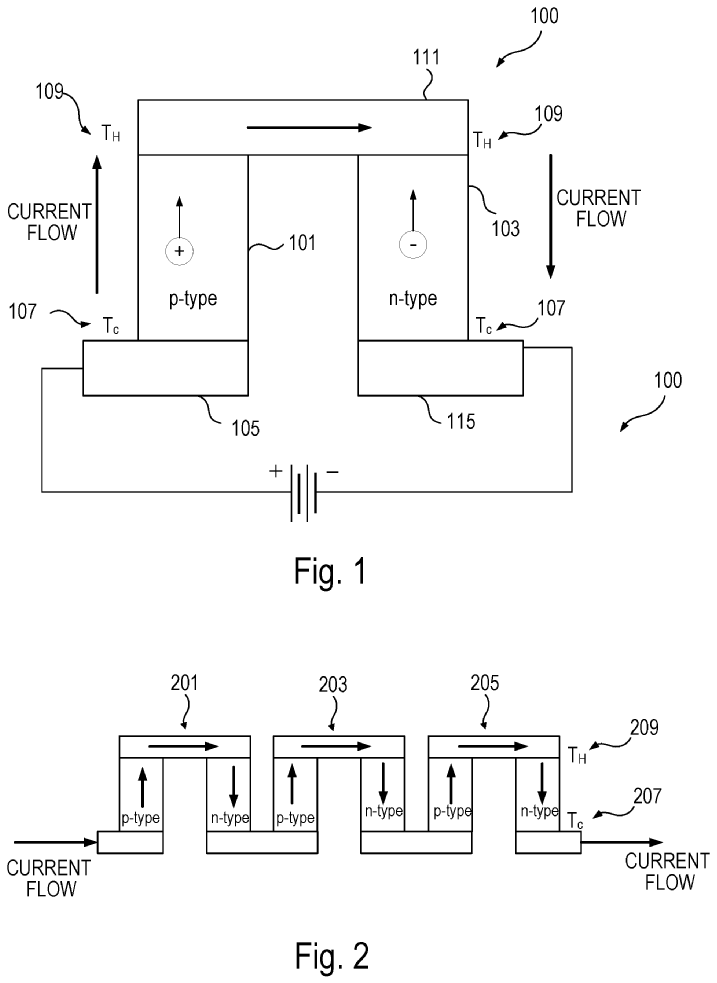

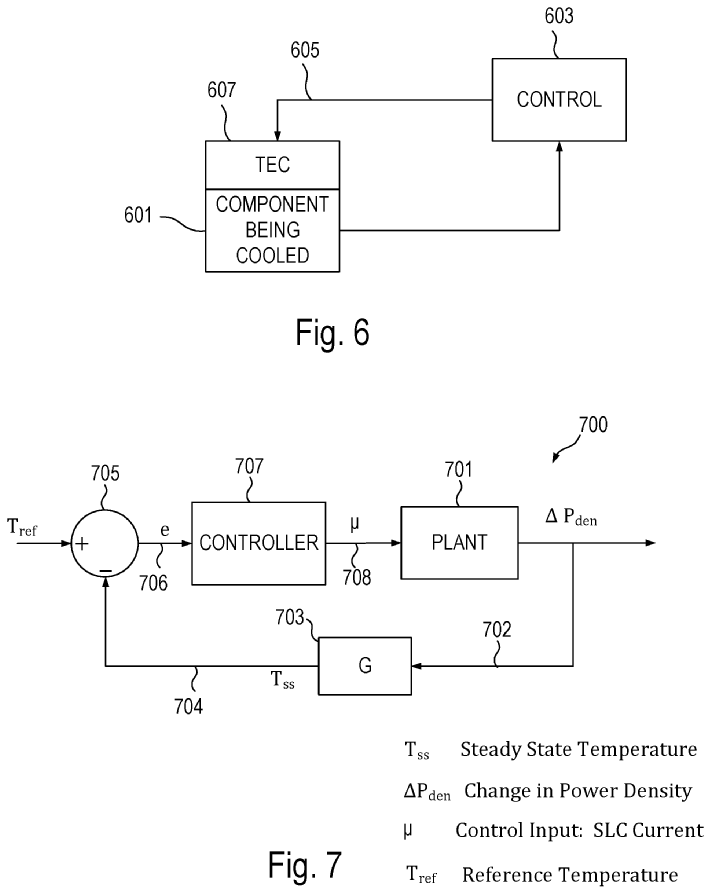

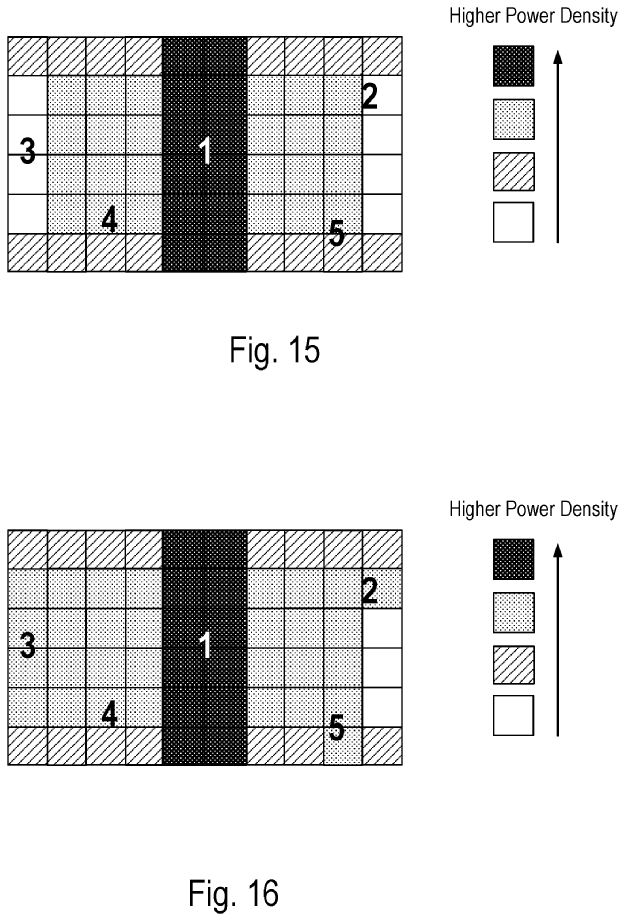

Patent: Runtime localized cooling of high-performance processors - AMD

Patent: Runtime localized cooling of high-performance processors - AMD

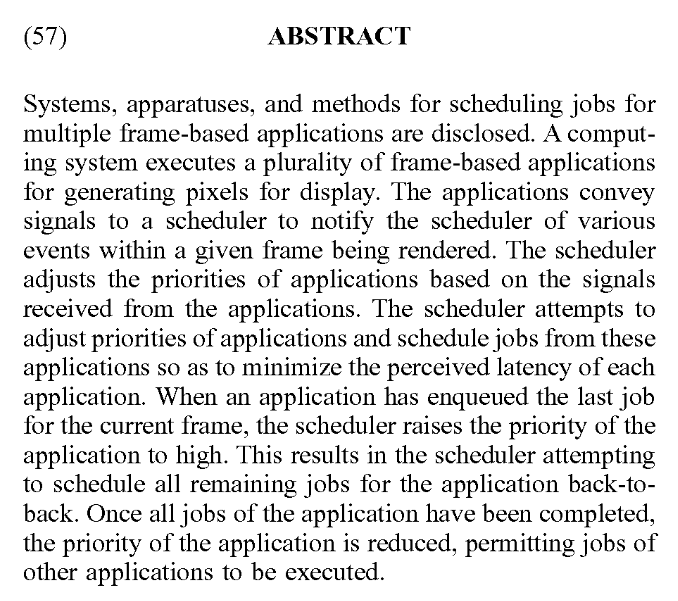

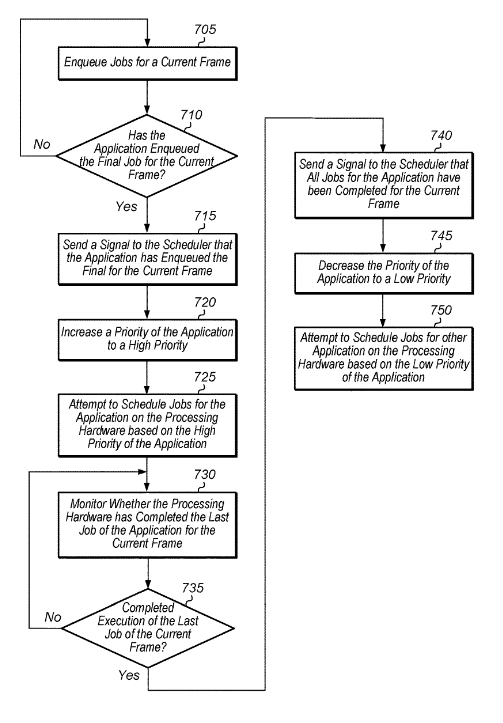

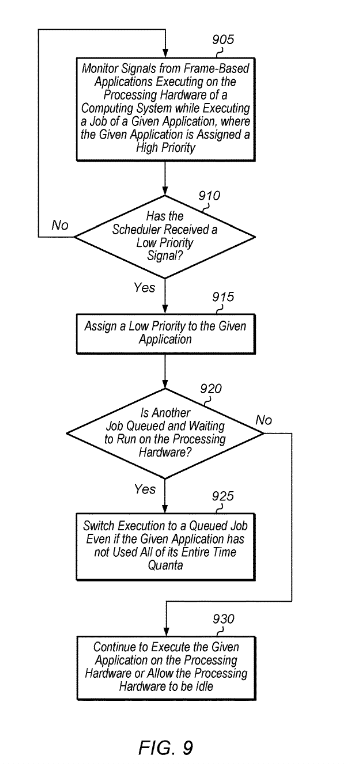

Patent: Multiple Application Cooperative Frame-based GPU Scheduling - AMD

Patent: Multiple Application Cooperative Frame-based GPU Scheduling - AMD

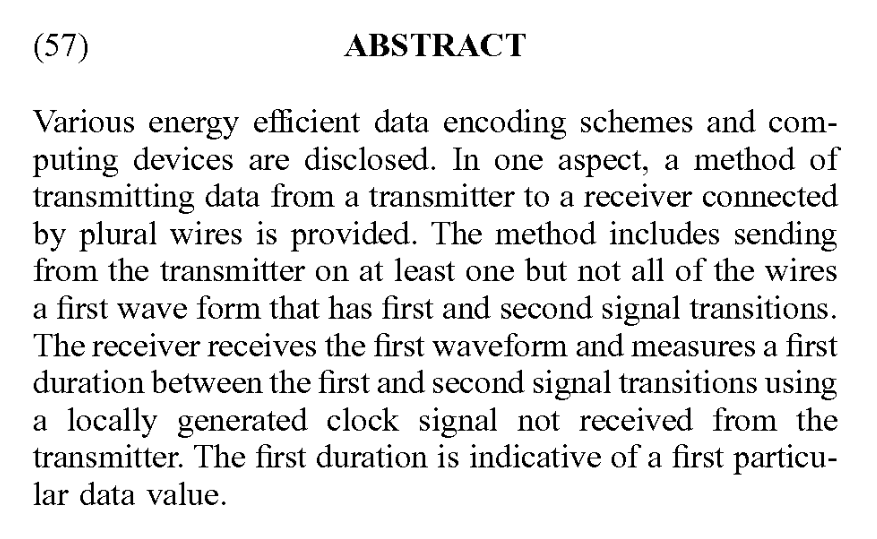

Patent: Energy Efficient Adaptive Data Encoding Method And Circuit - AMD

Patent: Energy Efficient Adaptive Data Encoding Method And Circuit - AMD

Patent: Molded die last chip combination - AMD

Patent: Molded die last chip combination - AMD

Patent: Even/odd die aware signal distribution in stacked die device - AMD

Patent: Even/odd die aware signal distribution in stacked die device - AMD