Infosec, RE, high speed digital, T&M, network hardware, microscopy, FPGA/ASIC, @IOActive, KD2HKV, #SoOthersMayLive. Lead dev of glscopeclient. Tweets are my own

How to get URL link on X (Twitter) App

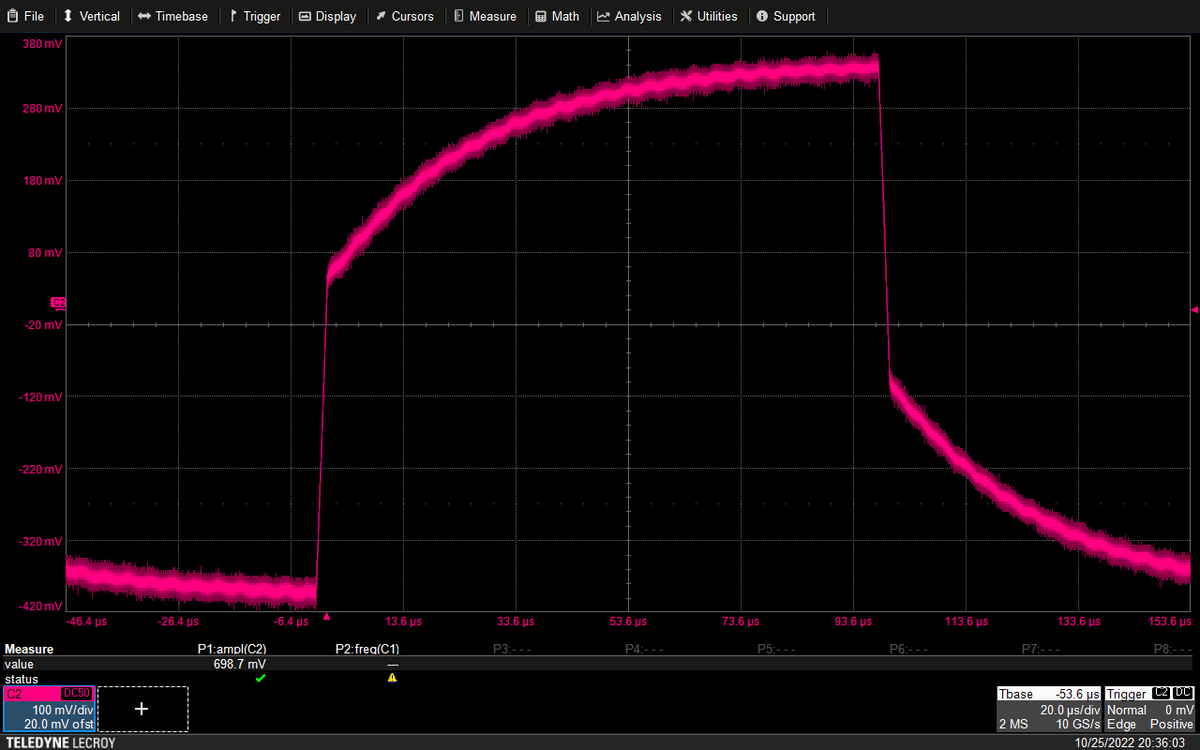

First step is low frequency trimming. This adjusts the DC path (OPA210) and AC path (BUF802) to have the same gain.

First step is low frequency trimming. This adjusts the DC path (OPA210) and AC path (BUF802) to have the same gain.

This model is mostly based on guesswork as I don't have a lot of details from their datasheet on internal construction (e.g. metal layer thicknesses).

This model is mostly based on guesswork as I don't have a lot of details from their datasheet on internal construction (e.g. metal layer thicknesses).

There's a barcode and QR code that seem to be printed using fairly ordinary black ink on paper, and then there's a special insert (the blue area) where Magic(tm) happens.

There's a barcode and QR code that seem to be printed using fairly ordinary black ink on paper, and then there's a special insert (the blue area) where Magic(tm) happens.

https://twitter.com/murrzbow/status/1467552481748176904Oh, and of course these geniuses are throwing a fancy TCXO on the board to get "low jitter" clocking.

Also, I really need to get a polarizer or something on this scope... the glare with shiny surfaces like this carbon tape is pretty extreme.

Also, I really need to get a polarizer or something on this scope... the glare with shiny surfaces like this carbon tape is pretty extreme.

@TeledyneLecroy The intended use is de-skewing of different probes: you terminate one end of the fixture, drive a fast edge into the other end, then place each probe at the same point on the fixture and adjust skew until you see the edge at the same point on the scope display.

@TeledyneLecroy The intended use is de-skewing of different probes: you terminate one end of the fixture, drive a fast edge into the other end, then place each probe at the same point on the fixture and adjust skew until you see the edge at the same point on the scope display.

First off, the PCF200 test fixture I had been using for solderless testing seems to be a limiting factor in performance. More loss and worse ripples.

First off, the PCF200 test fixture I had been using for solderless testing seems to be a limiting factor in performance. More loss and worse ripples.

This is absolutely not what I bought the scope for, but it really shows off the capabilities of the optics.

This is absolutely not what I bought the scope for, but it really shows off the capabilities of the optics.

Planned prototype specs: one channel, 500 MHz / 5 Gsps / 12 bits, 50 ohm SMA input, dual channel DDR3 SODIMM waveform memory.

Planned prototype specs: one channel, 500 MHz / 5 Gsps / 12 bits, 50 ohm SMA input, dual channel DDR3 SODIMM waveform memory.

Here's insertion loss. S21 (red), is the left pair going through the layer change, S43 (blue) is the right pair with no layer change.

Here's insertion loss. S21 (red), is the left pair going through the layer change, S43 (blue) is the right pair with no layer change.

Here's the service plenum with the access cover removed. I change the carbon filter annually and the HEPA only when I notice it's clogged enough to impair airflow.

Here's the service plenum with the access cover removed. I change the carbon filter annually and the HEPA only when I notice it's clogged enough to impair airflow.

https://twitter.com/azonenberg/status/1479957612556742656

So far, there's two known problems with it.

So far, there's two known problems with it.

It's a little hard to see in this view but the new design has 45 degree angled interior walls to provide a smooth transition between horizontal and vertical. This should provide better paint coverage and conductivity.

It's a little hard to see in this view but the new design has 45 degree angled interior walls to provide a smooth transition between horizontal and vertical. This should provide better paint coverage and conductivity.

The LFO can also be used to produce DC signals, so you get a free DC reference/bias voltage generator.

The LFO can also be used to produce DC signals, so you get a free DC reference/bias voltage generator.

All of this stuff lives inside a single large cabinet with bins mounted on internal rails.

All of this stuff lives inside a single large cabinet with bins mounted on internal rails.

@Applied_Ion First attempt at gluing the undamaged cap to a random scrap PCB with Crystalbond 509 failed with a cracked top. Can't let that happen to the real specimen!

@Applied_Ion First attempt at gluing the undamaged cap to a random scrap PCB with Crystalbond 509 failed with a cracked top. Can't let that happen to the real specimen!