Researcher-maker-hacker focusing on Computer Graphics with a #retro, #fpga gaming twist. Enjoys #3dprinting and #electronics. Created @iceslapp and #Silice.

How to get URL link on X (Twitter) App

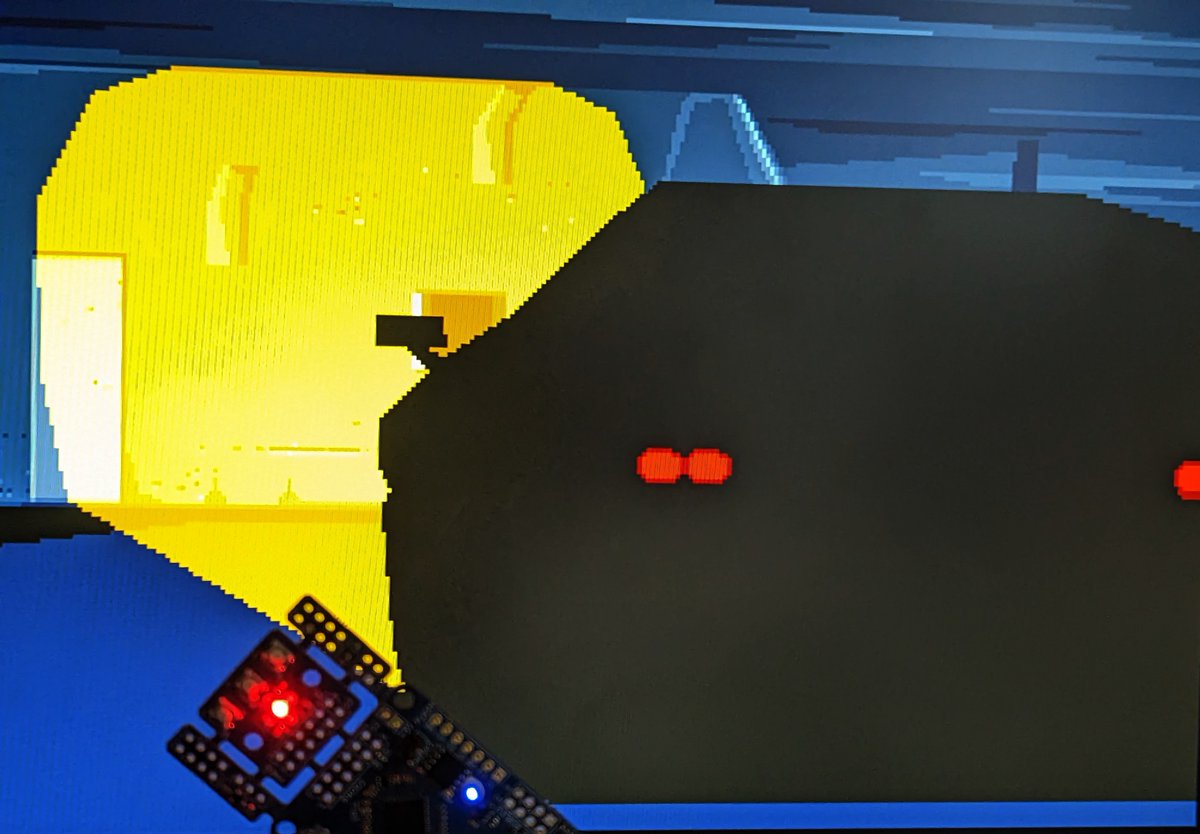

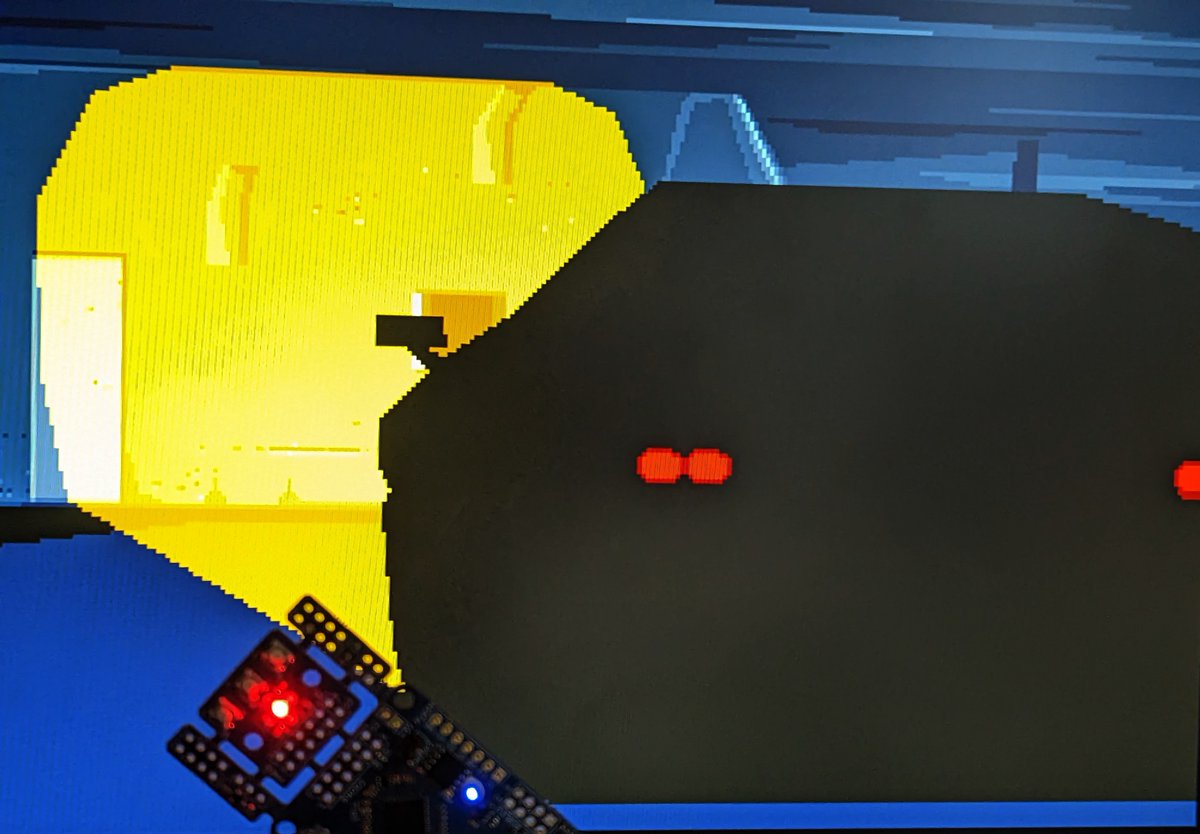

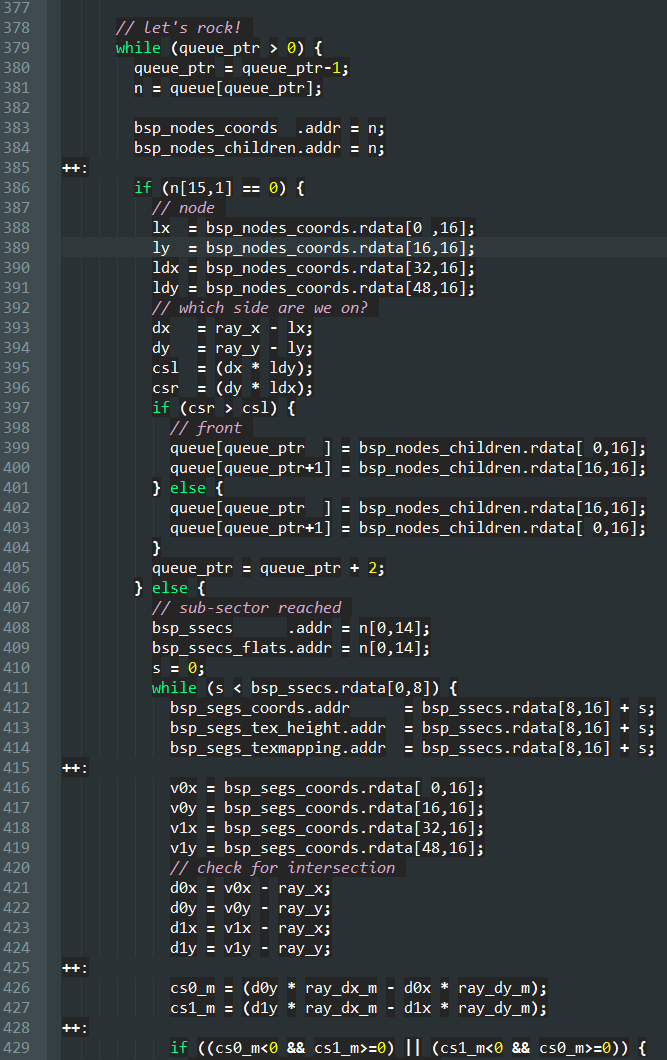

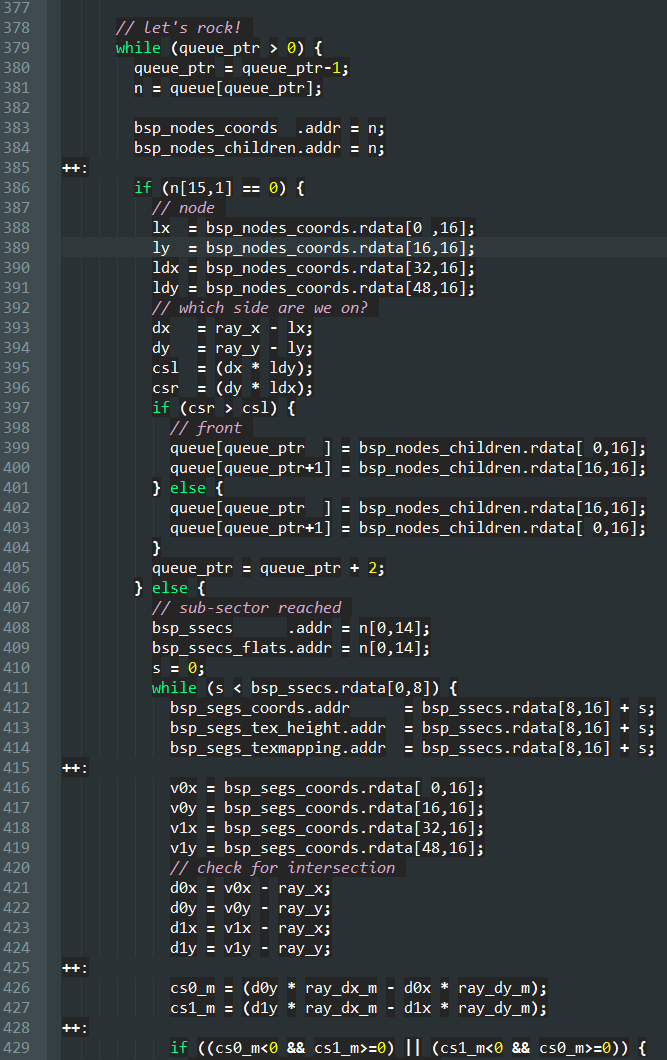

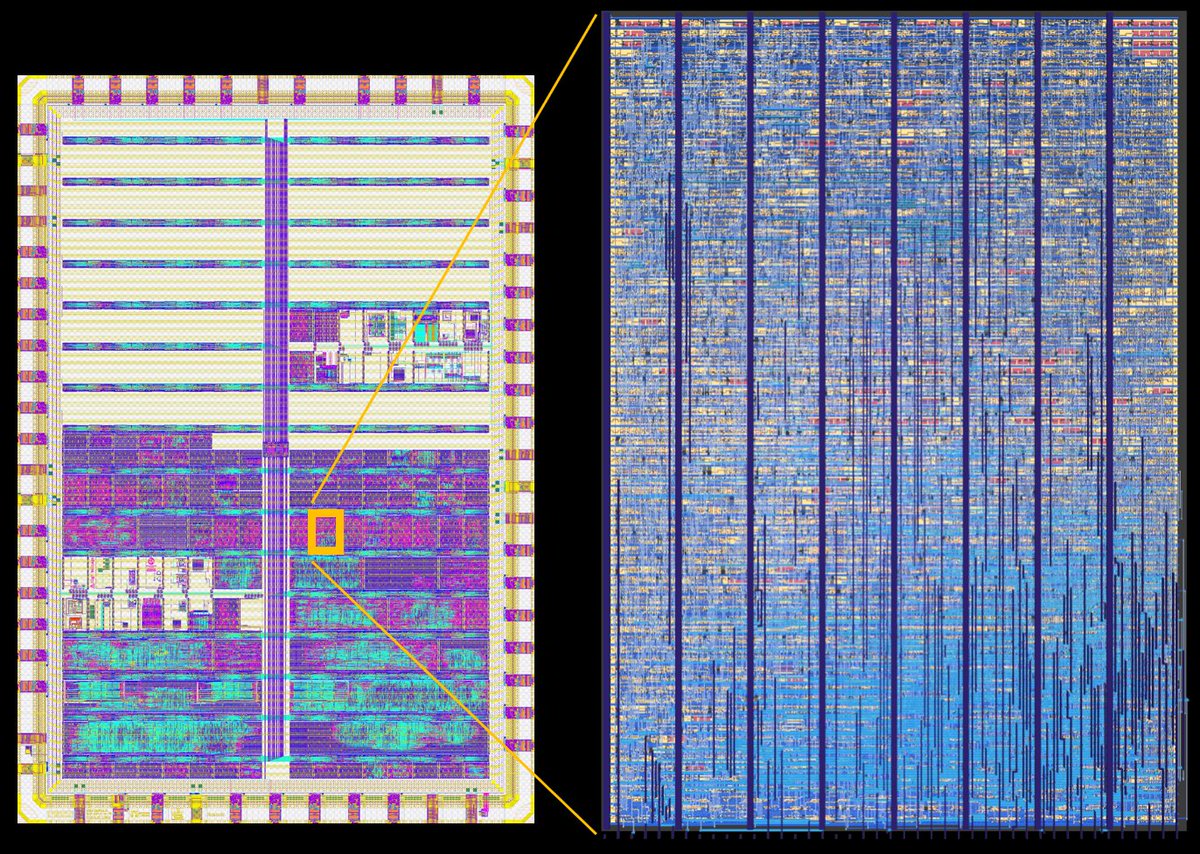

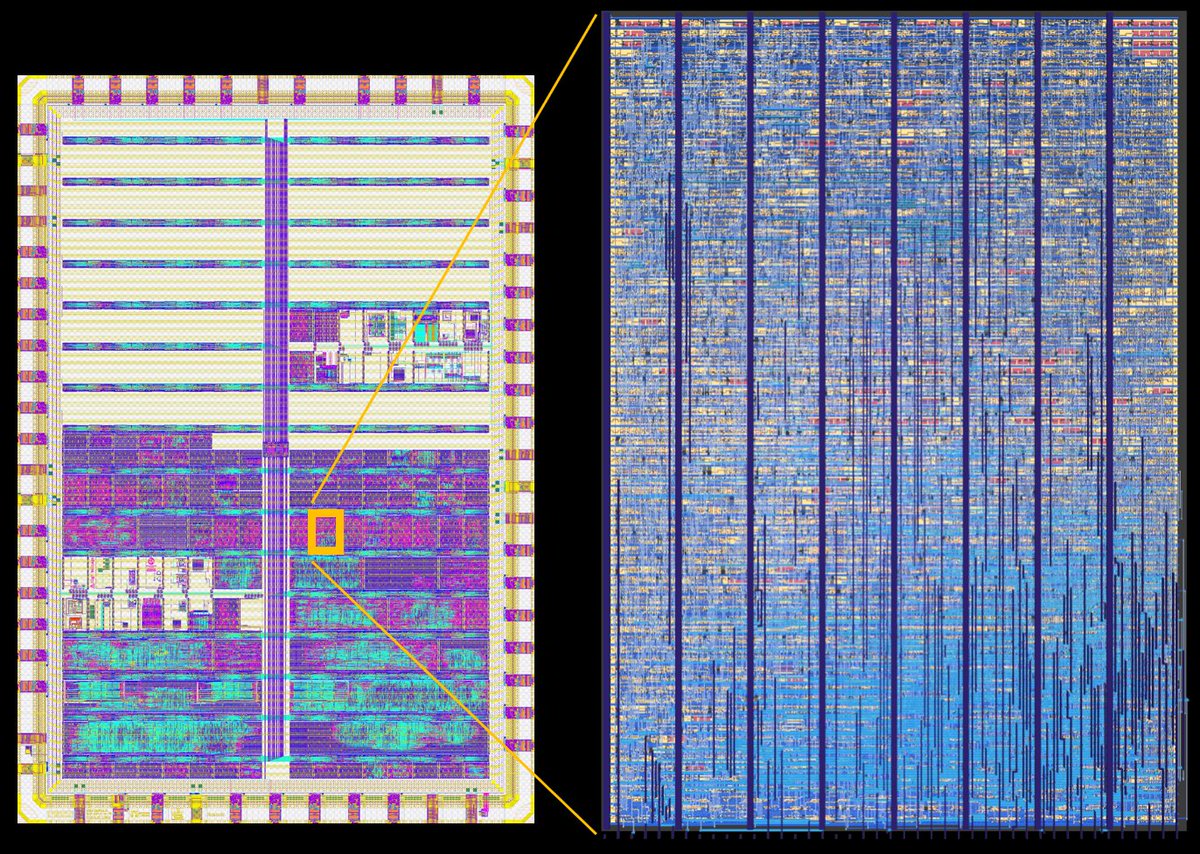

2/ The design is written in #Silice and exported to Verilog, and then synthesized to #ASIC through the amazing #TinyTapeout framework.

2/ The design is written in #Silice and exported to Verilog, and then synthesized to #ASIC through the amazing #TinyTapeout framework.