#IntelInvestorMeeting Thread - keynote presentations

I think someone exported this starting video at 720p.

I think someone exported this starting video at 720p.

Looks like it's an actual event with people on site.

Oh no

Oh no

Please can someone tell him that the word 'Torrid' doesn't translate to other english speaking countries the way he thinks it does

https://twitter.com/IanCutress/status/1493888546666655744

Torrid is a new word for 'English'.

No come on, please. Is this your blind spot? Really?

No come on, please. Is this your blind spot? Really?

Sometimes you have to tell your CEO where their blind spots are.

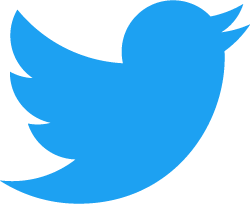

Only Intel can spread across all these

>The six business units are a good breakout. Does the Custom Compute for blockchain section become a 7th?

I'd write all the buzz words Pat is saying right now, but it's not needed.

1 trillion transistors per package by 2030.

@CerebrasSystems was doing that with wafer scale in 2020. Just some perspective here that some (well-funded) moonshots already exist.

@CerebrasSystems was doing that with wafer scale in 2020. Just some perspective here that some (well-funded) moonshots already exist.

PG: I helped create USB. My daughter plugs in a stick and says 'thank you papa'.

<silence in the room>

What was... that...?

<silence in the room>

What was... that...?

Based on this graph, USA never led?

USA CHIPS Act, EU CHIPS Act, Intel going after incentives

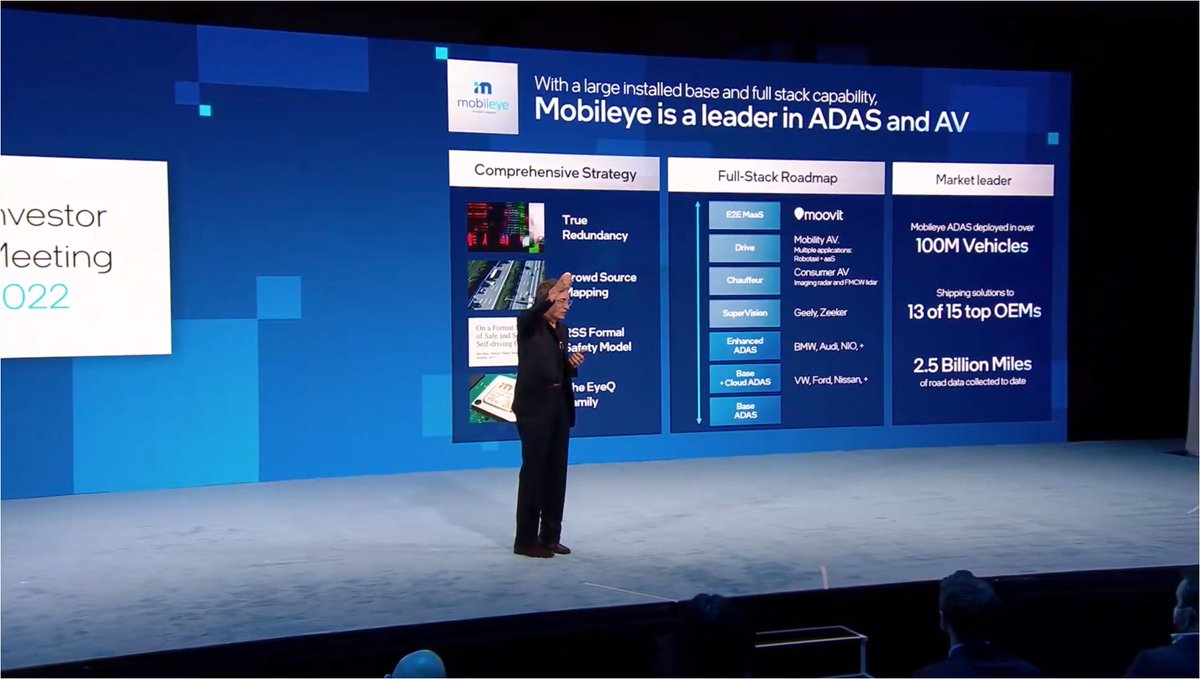

Pat says he wants one of the Mobileye cars. He's the CEO, why can't he have one?

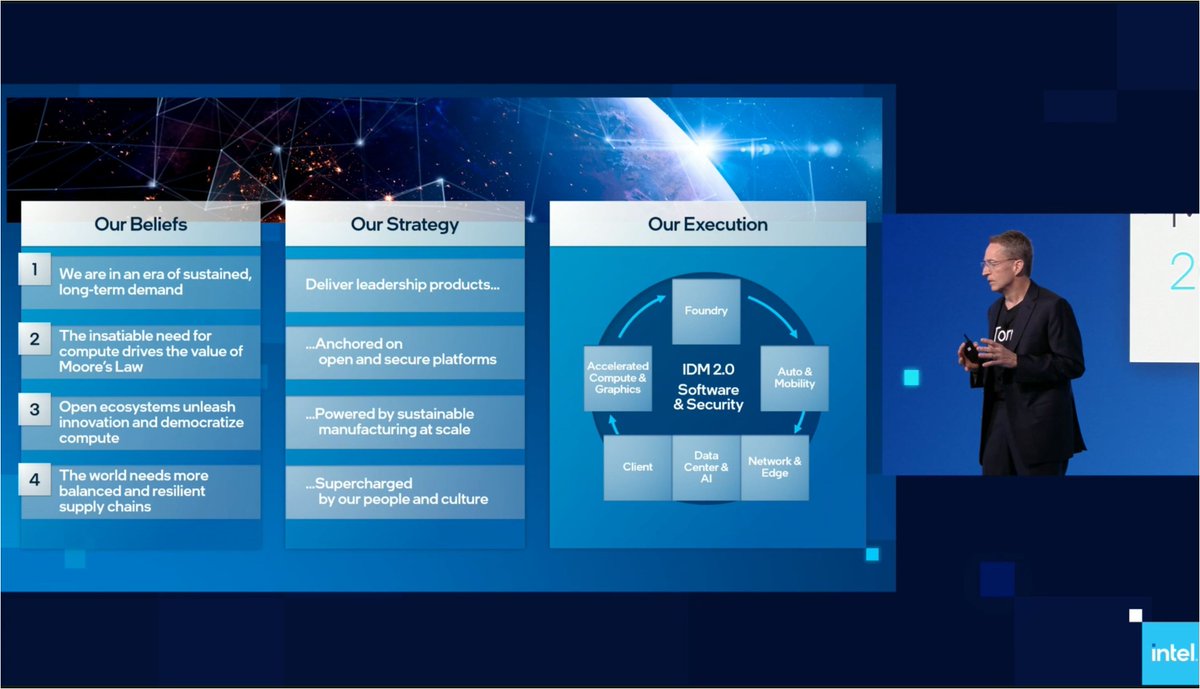

That's because all node updates become new numbers, rather than a +

Manufacturing has almost 'an unlimited budget' to get Intel back on track

PG: Grove used to say 'we gave you an unlimited budget and you still overspent'

<silence>

<silence>

Process Leadership is based on perf/watt. It's a very important distinction to remember

Meteor Lake hasn't taped out yet. Later this year.

PG: If you weren't amazed by Ann's presentation this morning, you're not a geek.

huh... what? Really? What is this statement?

huh... what? Really? What is this statement?

...aaaaand there's the religious reference.

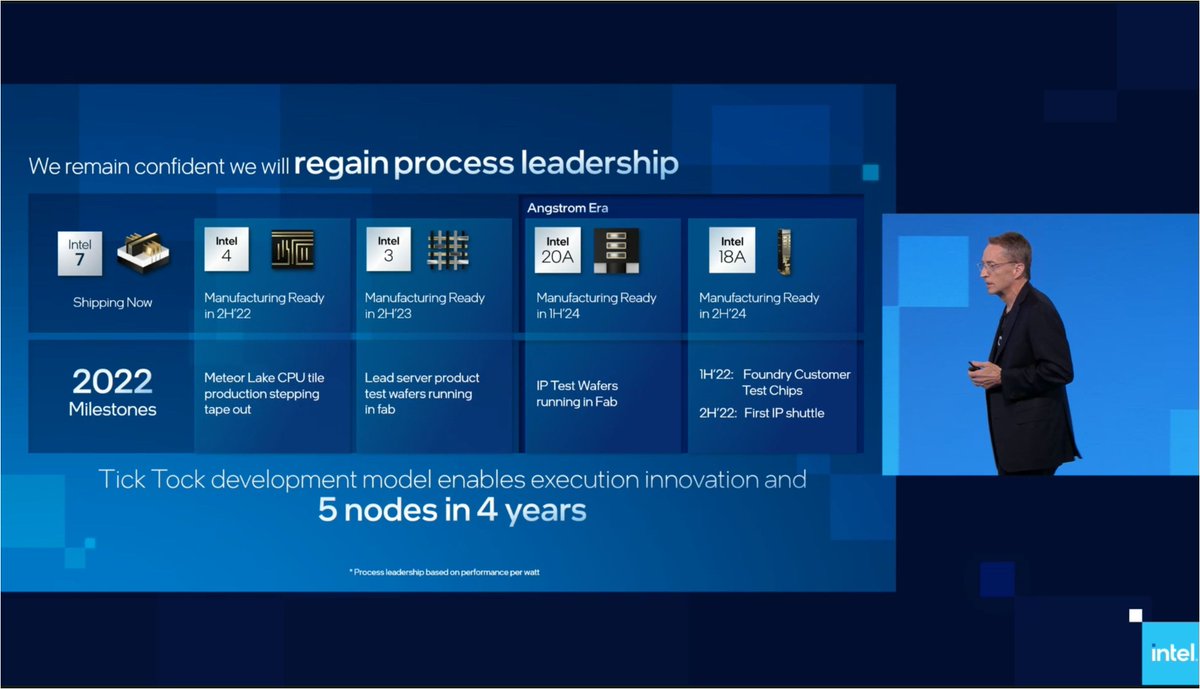

How much $ is Intel making from software today?

PG: The Best Team in the Industry

Did you hear that $TSM $NVDA $AMD Samsung

Did you hear that $TSM $NVDA $AMD Samsung

PG: 17k new employees in 2021. The Brain Drain is gone.

PG: We invented OKRs

what?

what?

PG: None of the following assumptions are heroic

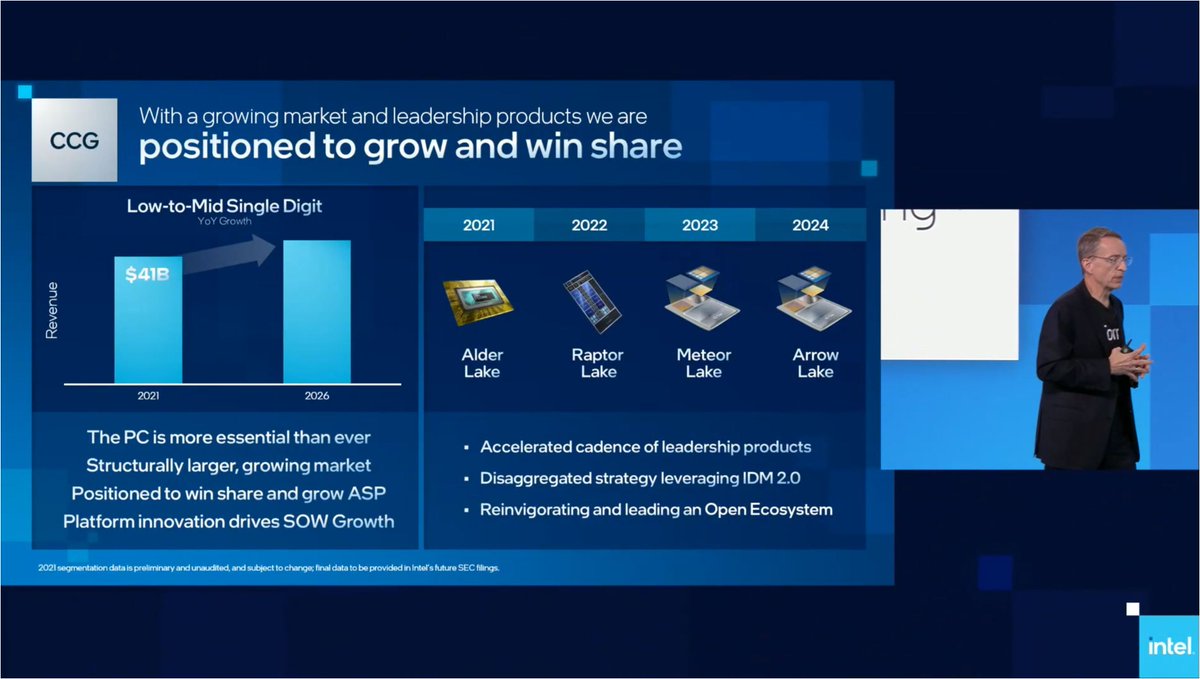

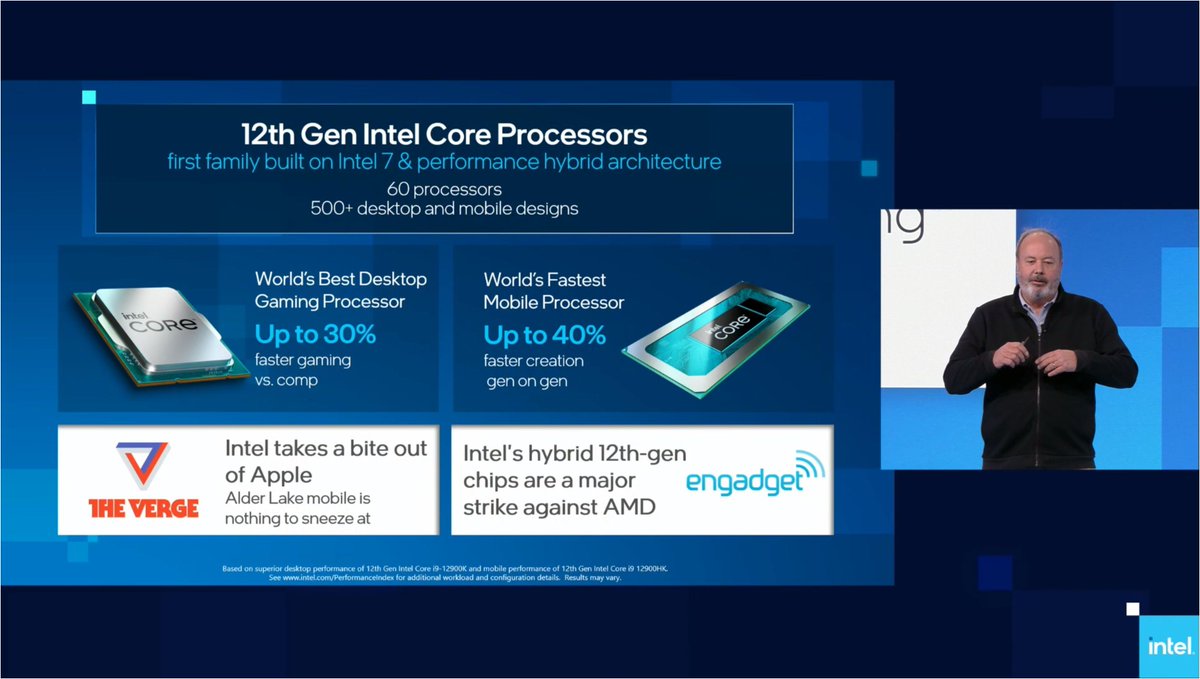

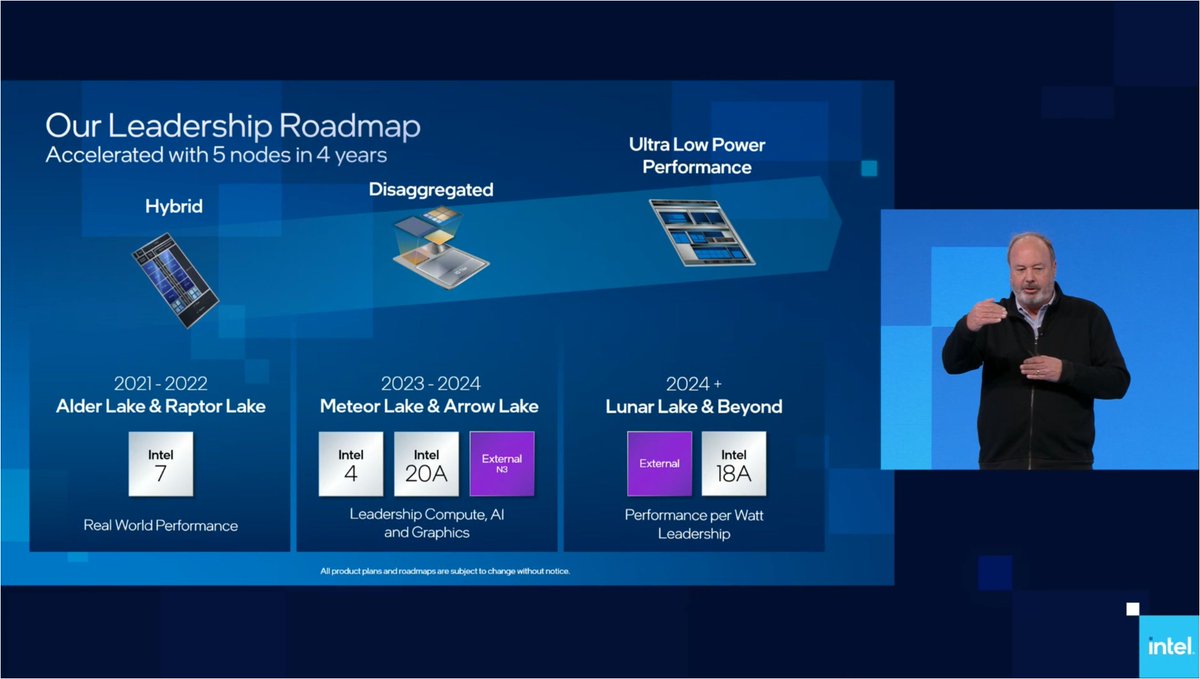

Alder Lake 12th Gen

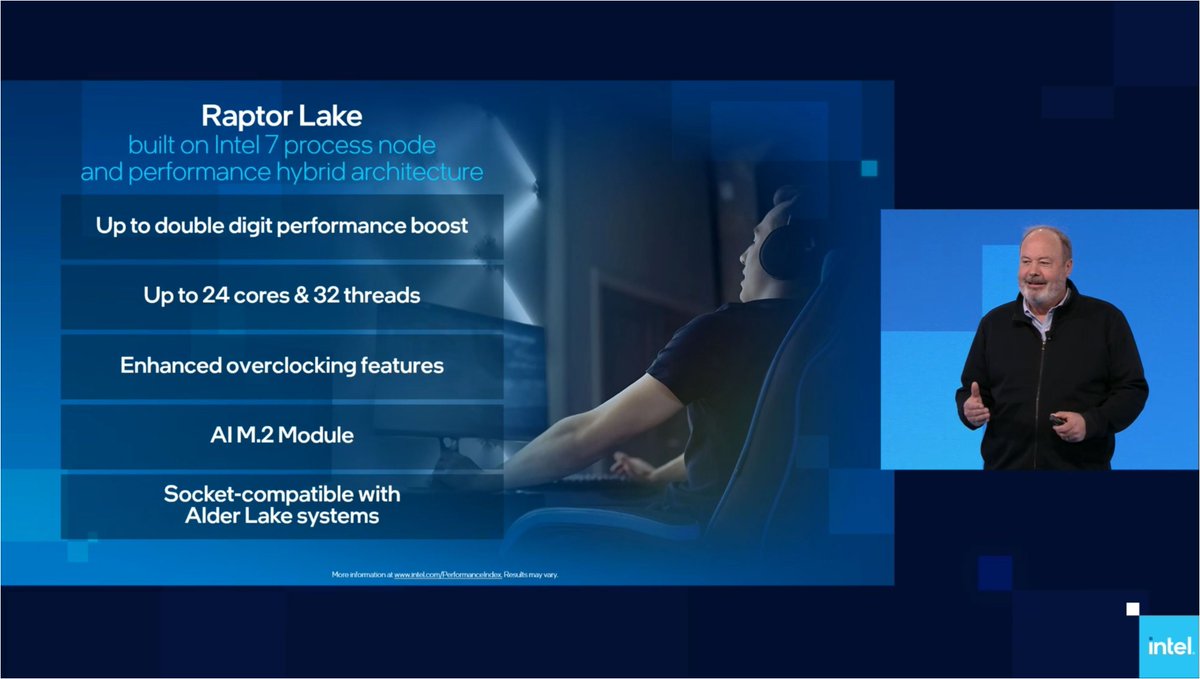

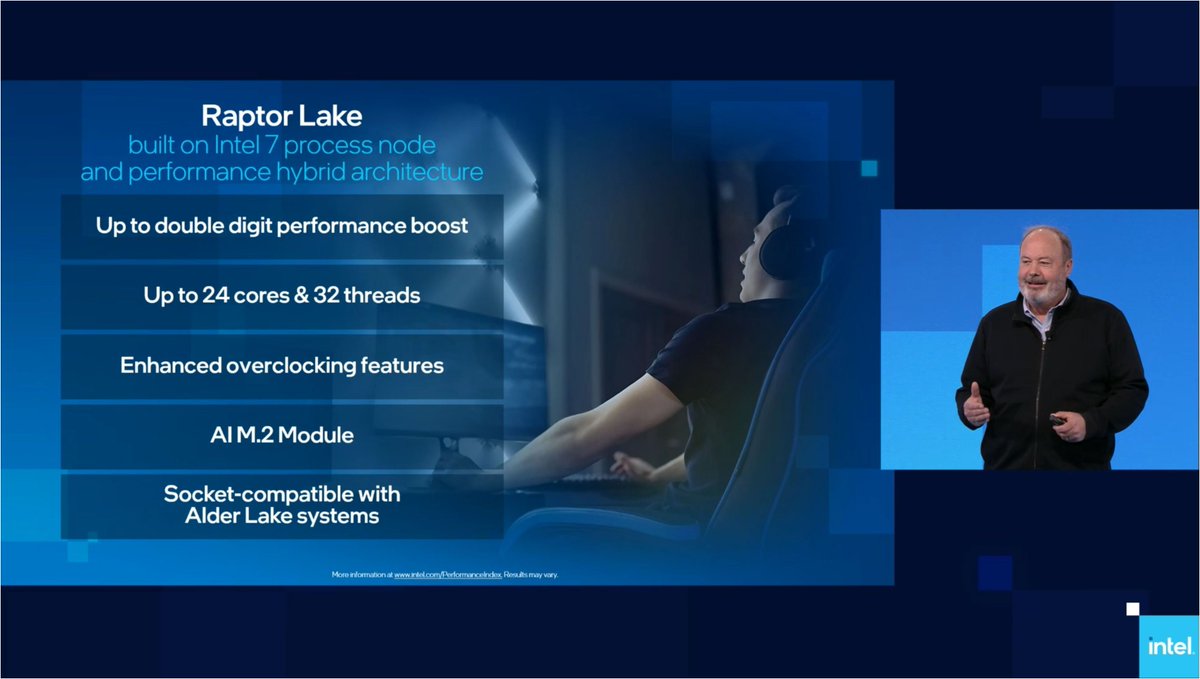

Raptor Lake 13th Gen

Meteor Lake 14th Gen

Arrow Lake 15th Gen

Raptor Lake 13th Gen

Meteor Lake 14th Gen

Arrow Lake 15th Gen

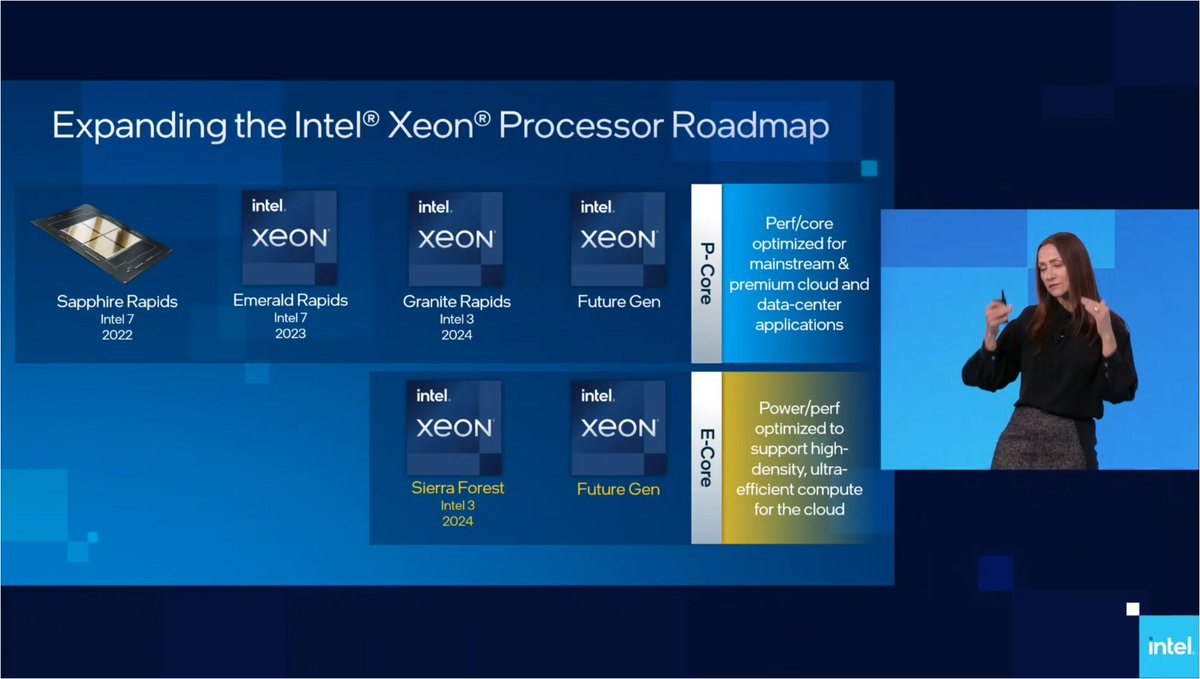

Sierra Forest is an all E-core version of Xeon for 2024

New platform every 2 years. New product every year.

Emerald Rapids will have increased core count, but feature compatible with Sapphire Rapids

Alder Lake leverages 'Hybrid' architecture

Pat then uses that as a point to mention that Xeon will do similar, but all P-core and all E-core. No Hybrid for Xeon

Pat then uses that as a point to mention that Xeon will do similar, but all P-core and all E-core. No Hybrid for Xeon

Intel 3 process node ?

PG: 2024 is an inflection point in competitiveness

PG: Shifting networking compute on dedicated silicon, leaving CPU free to do normal work

AXG Revenue in 2021 was $0.7B

AXG Revenue in 2022 will be >$1B

So 4m GPUs for 300m up to 1.3b (?). How much revenue per GPU?

AXG Revenue in 2022 will be >$1B

So 4m GPUs for 300m up to 1.3b (?). How much revenue per GPU?

PG: 'Business ain't fair'

PG: HPC has been niche for 40 years. Now is mainstream.

PG: Developer ecosystem is pumped

Falcon Shores. One CPU chiplet, two Xe chiplets. ? Or a central IO die with Xe GPU, and two CPU chiplets?

Strong pipeline of customers

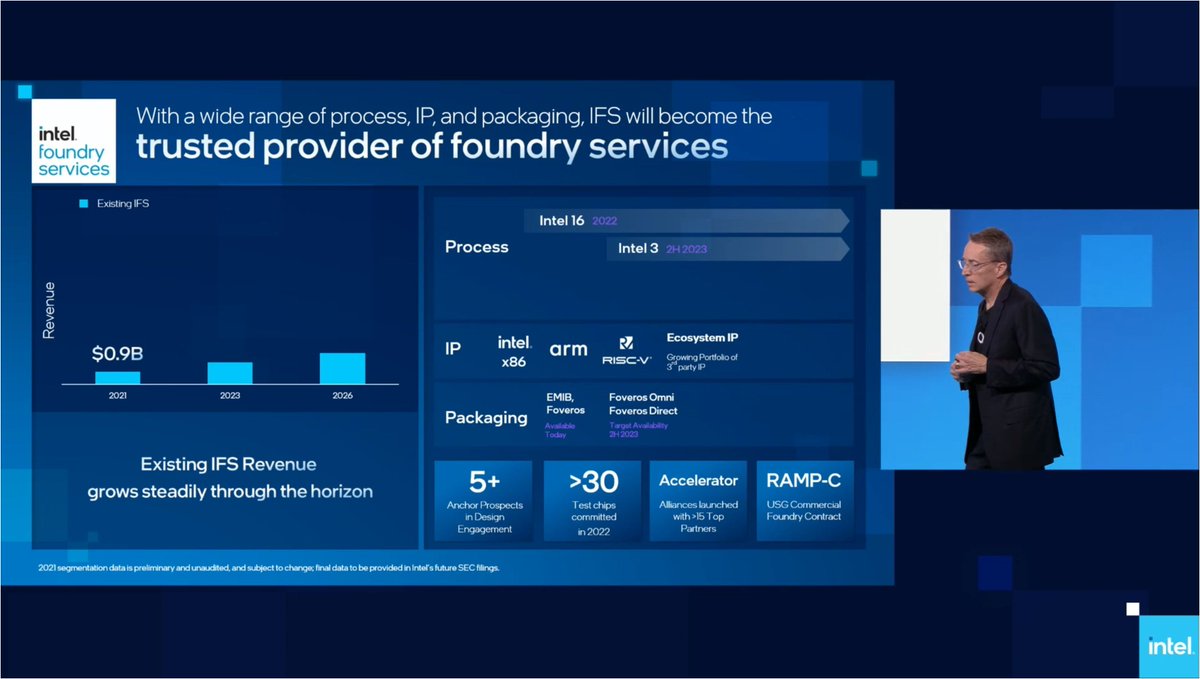

Already running 30+ different test chips in 2022

Already running 30+ different test chips in 2022

What's the scale on this revenue graph? Does is start at zero? So a 2x increase in revenue by 2026?

What annoys me about this is PG stating that IDM and IFS are always positive feedback loops. If it goes negative, then it speeds up that spiral

Intel going to run factories on nodes much longer, requires build out of new facilities.

PG doesn't mention that it means lots of demand. One of the biggest fears is that market does a downturn in demand. PG defends this, saying they can bring more in-house. That's not easy

PG doesn't mention that it means lots of demand. One of the biggest fears is that market does a downturn in demand. PG defends this, saying they can bring more in-house. That's not easy

For example, if that happened today, you can't simply build the TSMC N6 GPU on an Intel 7 process and expect the same result overnight. It's a 3-5 year process to shift products from fab to fab.

...who is prepaying? I mean, without MDF incentives

Pat teasing that CapEx intensity will decrease later in the decade.

What makes me think that if he wants to succeed, he can't let his foot off the gas.

What makes me think that if he wants to succeed, he can't let his foot off the gas.

PG: How do you know we are executing? We'll give you proof points with products on market and our roadmaps, like Alder Lake and Intel 7.

Me: That's not an answer. Those were in the pipe before you joined. Words are still words, not execution.

Me: That's not an answer. Those were in the pipe before you joined. Words are still words, not execution.

PG: Aim to double revenue and double Intel's multiple. A 4x of shareholder intel value.

So, $800b market cap?

So, $800b market cap?

Sandra Rivera @SandraLRivera to the stage, talking datacenter and AI

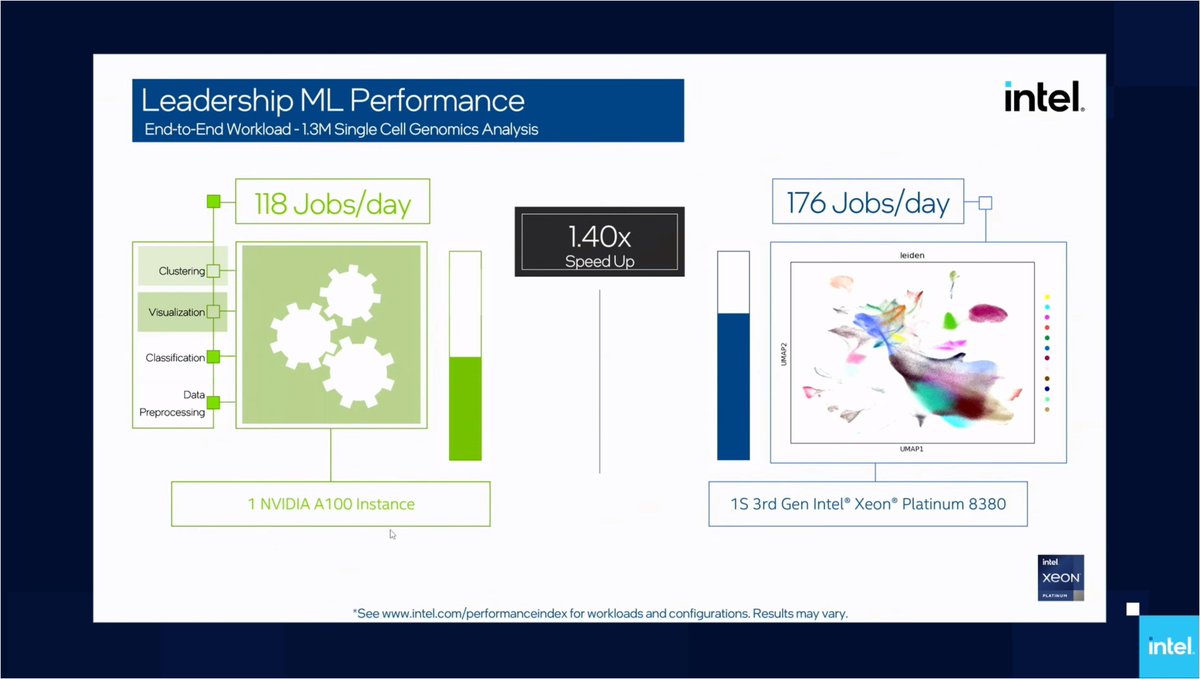

More Ice Lake Xeon CPUs shipped in December than AMD shipped all year.

Just don't ask about ASPs and GMs

Just don't ask about ASPs and GMs

The demo seems to not going well, they're showing the wrong videos

Intel: AI in the Xeon, no need for an Accelerator

Also Intel: But we'll also sell you an accelerator.

Also Intel: But we'll also sell you an accelerator.

SR: Intel 3 using higher density, higher performance libraries.

Which is it? high density, or high performance? Usually it's a scale. This is still FinFET based EUV, not GAA.

Which is it? high density, or high performance? Usually it's a scale. This is still FinFET based EUV, not GAA.

Intel can leverage its enterprise portfolio. No other company can do all of this at once. As a result, Intel is pushing combo Intel solutions for market value

Now explaining what SGX again. Is it SGX or TSX that's been talked about, implemented, disabled, implemented, etc

Michelle Johnston Holthaus to the stage @MJHolthaus EVP of CCG

@MJHolthaus Number of PCs per household is increasing

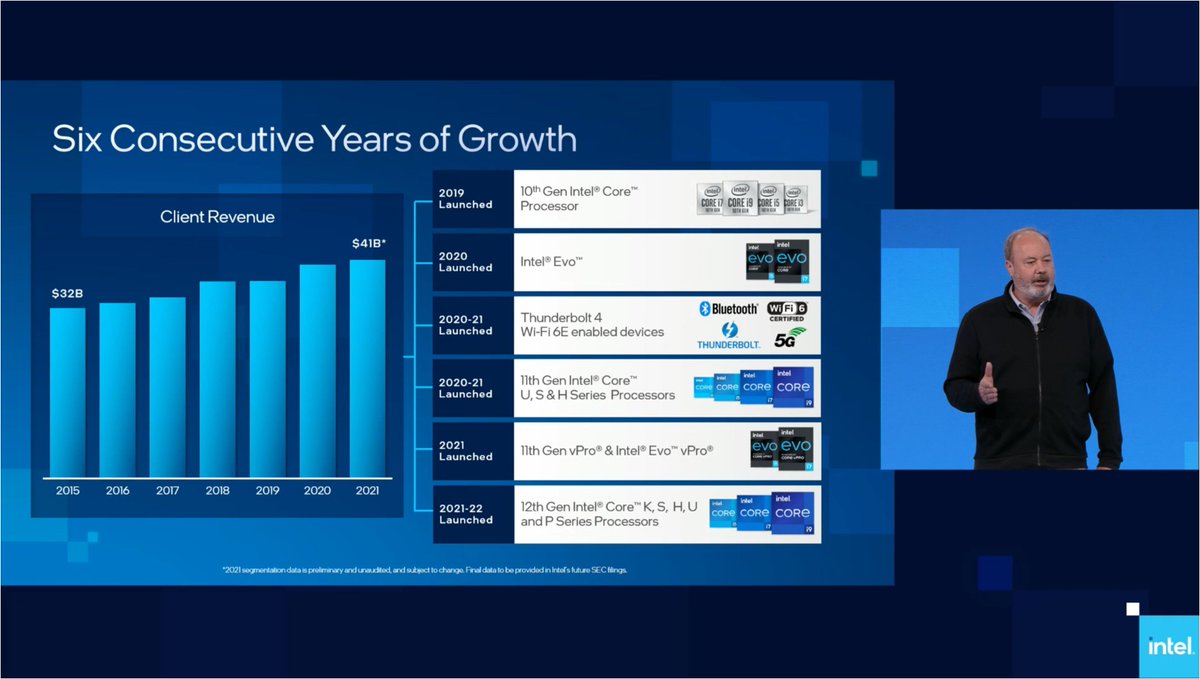

Client revenue growing - still grew when Apple left and Intel divested two technologies (5G and memory?)

This graph is somewhat misleading. Plot back to 2018 when PCs were at a historic low. Are we really expecting >360m units per year for the next 5 years?

This confirms the Lunar Lake name then as well

Note that with Meteor and Arrow Lake, Intel won't have performance per watt leadership according to this

Back to Raptor Lake: Shipping 2H 22

OK 15-20 minute break. Then:

Financial

Panel Q&A

Drinks

That last one, only if you're on site. Or maybe not.

It's 11:30pm here. Not sure if I'll say awake.

Financial

Panel Q&A

Drinks

That last one, only if you're on site. Or maybe not.

It's 11:30pm here. Not sure if I'll say awake.

ok one more.

'People are worried about our low 50s Gross Margins. We have a path to strong mid 50s, high 50s'.

Wasn't the demand to push back to mid-to-high 60s?

'People are worried about our low 50s Gross Margins. We have a path to strong mid 50s, high 50s'.

Wasn't the demand to push back to mid-to-high 60s?

• • •

Missing some Tweet in this thread? You can try to

force a refresh