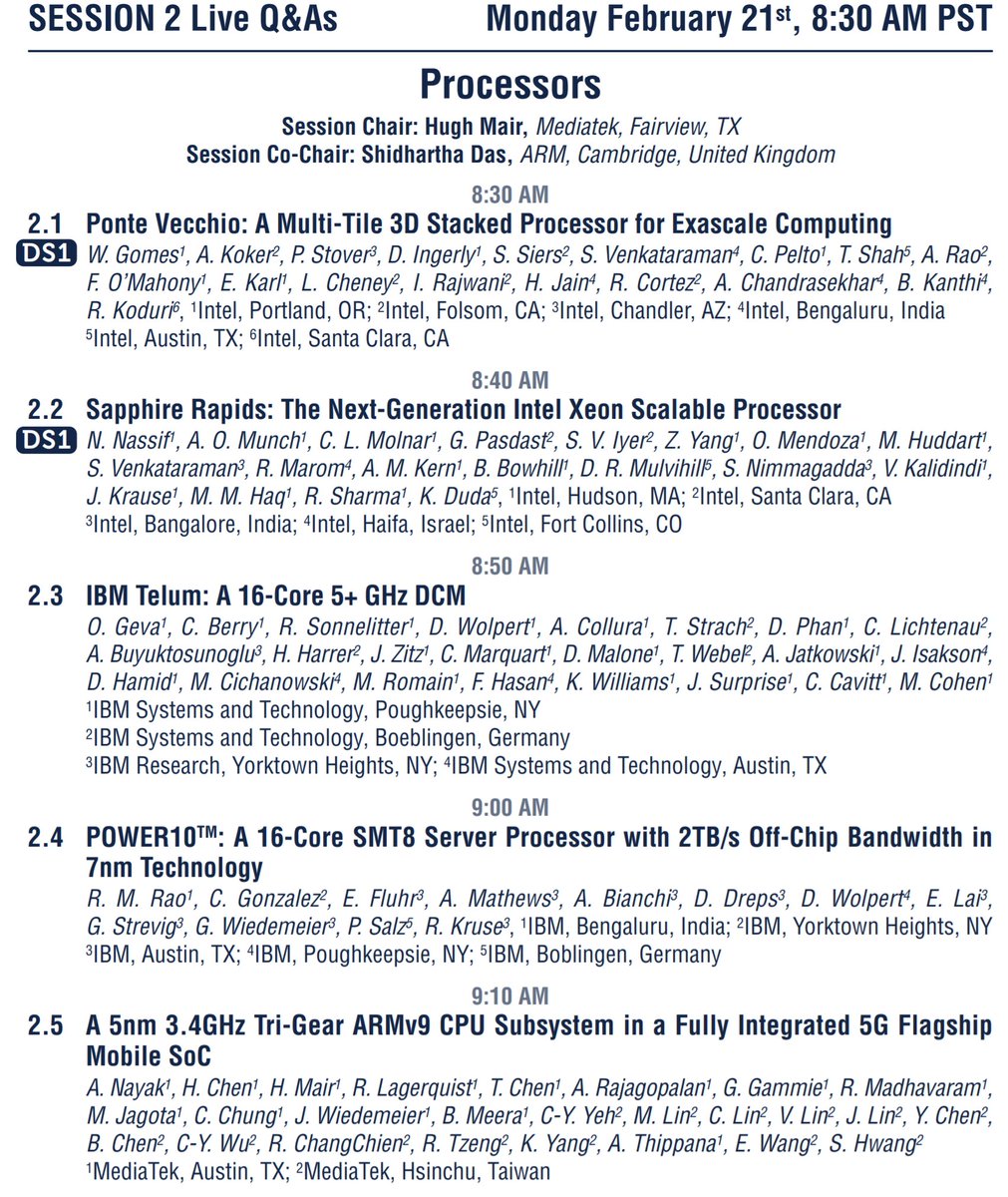

Story time! So yesterday a courier dropped off a package which was meant for next door. I accepted it, put it in the hallway, and notice it had the massive logo from my previous employer, Future. I thought it was odd, but I messaged my neighbour to collect it when they're in /1

2/ Neighbour comes over later today, I mention I left the company two weeks ago, and she says that she's just left the company too! The box was to put all the computer hardware in and send back. Turns out the company she worked for had been acquired by Future back in November

3/ So technically my neighbour and I worked at the same company for 4 months without realising. She had left because they cut the team from 12 down to 4, but also increased the workload. Found a better offer elsewhere.

4/ It's also worth noting at the same time I left, I know 2 other people that also left. This makes 3, plus me is 4. Seems to be a high amount of turnover.

But it's a small world...!

But it's a small world...!

5/ For everyone waiting to hear about my next gig, I promise soon. Just finalizing paperwork and wanting to get _everything_ squared away before announcing. But it's already starting - meetings after meetings, and several flights booked for North America already

• • •

Missing some Tweet in this thread? You can try to

force a refresh