Intel EU Announcement Webcast is starting. #tweetthread

'Strong partnerships in EU' Endless possibilities

...and the stream has stopped for me

80b euros in foundry, packaging, and services. Phase 1, 17b euro leading edge megasite in germany. Expansion in Ireland with 12b

Italy, Poland, Spain.

80% of chips in Asia. This pan european investment addresses that balance.

EU will get the most advanced technologies

EU will get the most advanced technologies

Need to strengthen EU home-grown assets, aim for 20% of world production by 2030

EU to break 3nm node barrier with new technologies

It's not just a few big fabs, it's mobilizing the best of Europe. Fundamentals to market applications. Need a network of research institutes, production, packaging, everywhere on the content. Whole of EU approach. Massive investment.

43b euro in EU Chips Act to 2030

Intel is the first major achievement of the EU Chips Act

Using strong local partners

>What are the chances Intel will want it all for themselves?

EU is ready for this.

>EU has ASML, CEA-Leti, Soitec, imec, etc

>EU has ASML, CEA-Leti, Soitec, imec, etc

Intel is committed to taking a pivotal role in shaping the EU semi future

Using most advanced transistor technologies.

Work ahead to get permits and financial support

>THIS

>THIS

Start making chips in 2027

Intel + Italy negotiations, 4.5b euro for 1500 intel jobs for start of the art back-end manufacturing. First of its kind in EU

Tower + STmicro have an agreement with a fab in Italy. This helps expand that.

Bringing supply chain parts together in EU.

EU is home to world class research instructions and companies. Linking investments to Intel's manufacturing plans.

Main Intel EU foundry design center in France too

Increasing lab space in Gdansk Poland by 50%.

Collab with BSC on Exascale and Zettascale. Joint labs to advance computing

Collab with BSC on Exascale and Zettascale. Joint labs to advance computing

'a pan-EU initiative'

> I hope he doesn't use the word Torrid here. The US definition doesn't work here.

Intel has spent 10b euros in EU suppliers. Double by 2026.

This isn't just investment, this sounds mostly like purchasing.

This isn't just investment, this sounds mostly like purchasing.

In terms of partner videos in the partner video segment, we had imec only. The rest were lots of politicians. I'm surprised they could only get imec on camera...

...and that's it.

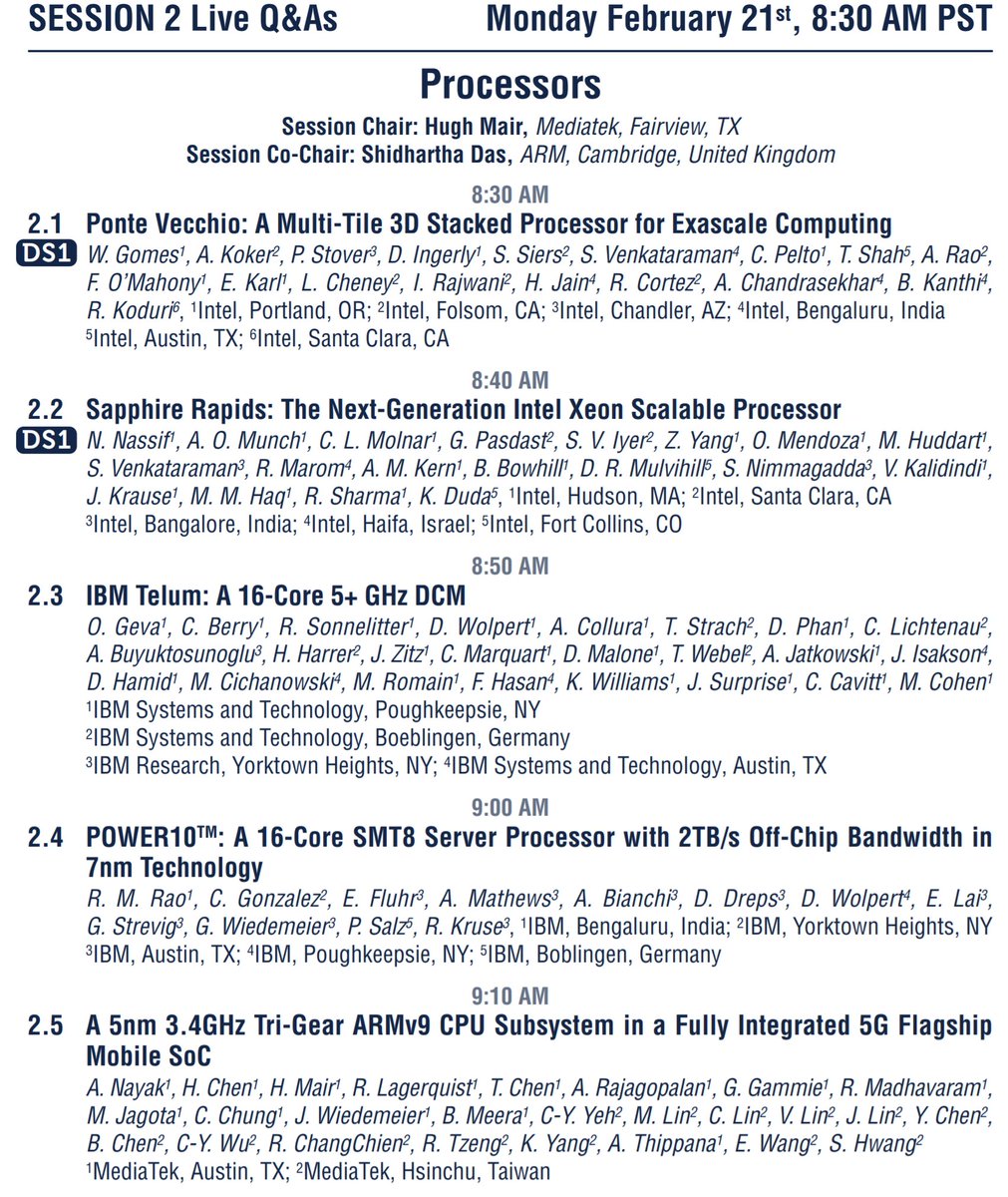

🇩🇪 €17b in Magdeburg ,

🇮🇪 €12b in Ireland ,

🇫🇷 New R&D center and IFS center in France

🇮🇹 Talks with Italy + Tower + STmicro

🇵🇱 Expanding Polish design centers

🇪🇸 Exa/Zetta with Barcelona Supercomputer

💰 €80b investment by 2030

💰 EU Chips Act is €43b

🇩🇪 €17b in Magdeburg ,

🇮🇪 €12b in Ireland ,

🇫🇷 New R&D center and IFS center in France

🇮🇹 Talks with Italy + Tower + STmicro

🇵🇱 Expanding Polish design centers

🇪🇸 Exa/Zetta with Barcelona Supercomputer

💰 €80b investment by 2030

💰 EU Chips Act is €43b

• • •

Missing some Tweet in this thread? You can try to

force a refresh